# Precise Measurement-Based Worst-Case Execution Time Estimation

#### DISSERTATION

submitted in partial fulfillment of the requirements for the degree of

# Doktor der technischen Wissenschaften (Dr. techn.)

by

#### Michael Zolda

| to the Faculty of Informatic<br>at Vienna University of Tec |                              |                            |

|-------------------------------------------------------------|------------------------------|----------------------------|

| Advisor:: PrivDoz. DiplIr                                   | g. Dr. techn. Raimund Kirner |                            |

|                                                             |                              |                            |

| This dissertation has been r                                | eviewed by:                  |                            |

|                                                             |                              |                            |

|                                                             |                              |                            |

|                                                             | (PrivDoz. DiplIng.           | (ao.UnivProf. DiplIng.     |

|                                                             | Dr. Raimund Kirner)          | Dr. techn. Peter Puschner) |

|                                                             |                              |                            |

| Vienna, September 2012                                      |                              | (Michael Zolda)            |

|                                                             |                              | ( )                        |

# Erklärung zur Verfassung der Arbeit

| Michael Zolda |         |        |      |

|---------------|---------|--------|------|

| Rögergasse 22 | / TOP 2 | A-1090 | Wien |

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen – die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

| (Ort, Datum) | (Michael Zolda) |

|--------------|-----------------|

# Abstract

A real-time computer system is a computer system in which the correctness of the system behavior depends not only on the logic results of the computations, but also on the physical instant at which these results are produced. Today, most real-time computer systems are implemented as collections of software tasks that are executed concurrently on a suitable hardware platform consisting of one or multiple microprocessors or microprocessor cores. Obtaining the worst-case execution time (WCET) of each real-time task is an essential step in ensuring the correctness of such a system.

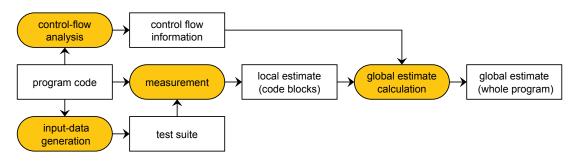

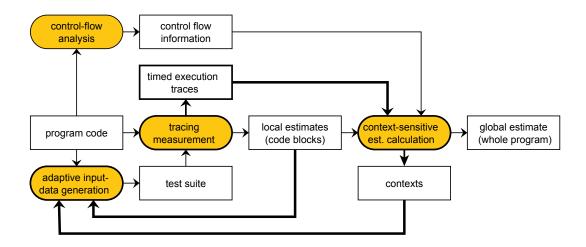

Measurement-based timing analysis (MBTA) is an easily retargetable analysis approach for estimating the WCET of a given task running on a particular target platform. In this approach, the execution times of individual task fragments are measured while the task is being executed on the intended target hardware. The observed local execution times of the individual task fragments are subsequently combined into a global WCET estimate for the task as a whole.

Industry demands WCET estimates that are close to the actual WCET. To fulfill this requirement, we must limit two opposed influences on the closeness of WCET estimates obtained by MBTA: (1) conservative WCET estimate calculation, otherwise known as pessimism, and (2) incomplete measurement coverage, also known as optimism.

Preliminary versions of individual research results found in this thesis have been published in various scientific formats. In this thesis I strengthen the following original contributions:

**Context-sensitive IPET:** I discuss context-sensitive IPET as a strategy for reducing the pessimism found in standard IPET.

Integration of methods: I discuss how the methods for reducing optimism and pessimism that have been developed within the FORTAS project have been tied together to form a complete MBTA approach that can provide closer WCET estimates than possible with standard MBTA approaches.

**Experimental evaluation:** I present an experimental evaluation of the FORTAS approach. The results indicate the effectiveness of the approach. Most importantly, the evaluation includes a quantitative comparison between analysis results obtained by the FORTAS tool and the corresponding results of the industrial-strength static WCET analysis tool AIT.

# Kurzfassung

Ein Echtzeitcomputersystem ist ein Computersystem, bei dem die Korrektheit des Systemverhaltens nicht nur von den logischen Berechnungsergebnissen abhängt, sondern auch vom physikalischen Zeitpunkt, zu dem die Resultate erzeugt werden. Heutzutage werden die meisten Echtzeitcomputersysteme als Ansammlungen von Software-Tasks implementiert, welche parallel auf einer passenden Hardware-Plattform mit einem oder mehreren Mikroprozessoren oder Mikroprozessorkernen ausgeführt werden. Das Ermitteln der Worst-Case Execution Time (WCET) der einzelnen Echtzeit-Tasks ist ein essentieller Schritt bei der Sicherstellung der Korrektheit eines solchen Systems.

Die Messbasierte Zeitanalyse (MBTA) ist ein einfach retargierbarer Ansatz zur Abschätzung der WCET eines gegebenen Tasks, der auf einer bestimmten Hardware-Plattform ausgeführt wird. Bei diesem Ansatz werden die Ausführungszeiten einzelner Task-Fragmente gemessen, während der Task auf der vorgesehenen Target-Hardware ausgeführt wird. Die beobachteten lokalen Ausführungszeiten werden anschließend zu einer globalen WCET-Abschätzung für den Gesamt-Task zusammengesetzt.

Die Industrie fordert WCET-Abschätzungen, die nahe an der tatsächlichen WCET liegen. Um diese Forderung zu erfüllen, müssen wir zwei gegensätzliche Einflüsse auf die Nähe der mit MBTA ermittelten WCET-Abschätzungen beschränken: (1) die konservative Berechnung von WCET-Abschätzungen, bekannt als Pessimismus, und (2) die unvollständige Messabdeckung, bekannt als Optimismus.

Vorläufige Versionen einzelner Forschungsergebnisse in dieser Dissertation wurden bereits im Rahmen unterschiedlicher wissenschaftlicher Formate publiziert. In dieser Dissertation erweitere ich die folgenden originären Beiträge:

Kontextsensitives IPET: Ich diskutieren kontextsensitives IPET als Strategie zur Verringerung des Pessimismus in Standard-IPET.

Integration von Methoden: Ich diskutiere, wie die Methoden zur Verringerung von Optimismus und Pessimismus, die in Rahmen des FORTAS-Projekts entwickelt wurden, zu einem vollständigen MBTA-Ansatz zusammengefügt wurden, der nährere WCET-Abschätzungen liefern kann, als dies mit Standard-IPET-Ansätzen möglich ist.

Experimentelle Evaluierung: Ich stellen eine experimentelle Evaluierung des FOR-TAS-Ansatzes vor. Die Evaluierung umfasst insbesondere einen quantitativen Vergleich zwischen den Analyseergebnissen des FORTAS-Werkzeugs und der entsprechenden Analyseergebnisse des statischen WCET Analyseswerkzeugs AIT.

# Acknowledgment

The research on which this thesis is based has received funding from the IST FP-7 research project "Asynchronous and Dynamic Virtualization through performance ANalysis to support Concurrency Engineering (ADVANCE)" under contract no IST-2010-248828 and from the Austrian Science Fund (Fonds zur Förderung der wissenschaftlichen Forschung) within the research project "Formal Timing Analysis Suite of Real-Time Systems" (FORTAS-RT) under contract P19230-N13.

To the people who joined me on various parts of my journey.

# Contents

| C        | onten                           | ats                                                                                                                                                                                                           | ix                                   |

|----------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 1        | The 1.1 1.2 1.3 1.4 1.5 1.6 1.7 | Sis Overview  What is the WCET?  Why do we need WCET Estimates?  Traditional Methods for WCET Estimation  Measurement-based Timing Analysis (MBTA)  Use Cases for MBTA  Optimism and Pessimism  Contributions | 1<br>1<br>2<br>2<br>3<br>4<br>6<br>8 |

|          | 1.8                             | Guide to this Thesis                                                                                                                                                                                          | 9                                    |

| <b>2</b> | Rea                             | l-time Computer Systems                                                                                                                                                                                       | <b>13</b>                            |

|          | 2.1                             | What is a Real-Time Computer System?                                                                                                                                                                          | 14                                   |

|          | 2.2                             | Design Options                                                                                                                                                                                                | 17                                   |

|          | 2.3                             | Dependability and the Development Process                                                                                                                                                                     | 19                                   |

|          | 2.4                             | The Task Abstraction                                                                                                                                                                                          | 21                                   |

|          | 2.5                             | Task Scheduling on Uniprocessors                                                                                                                                                                              | 22                                   |

|          | 2.6                             | Task Scheduling on Multiprocessors and Recent Trends                                                                                                                                                          | 25                                   |

|          | 2.7                             | Chapter Summary                                                                                                                                                                                               | 26                                   |

| 3        | $\mathbf{WC}$                   | ET Analysis                                                                                                                                                                                                   | 29                                   |

|          | 3.1                             | WCET Analysis of Real Software                                                                                                                                                                                | 30                                   |

|          | 3.2                             | Microarchitectures                                                                                                                                                                                            | 33                                   |

|          | 3.3                             | The Computer State                                                                                                                                                                                            | 35                                   |

|          | 3.4                             | The Implementation of System Behavior                                                                                                                                                                         | 39                                   |

|          | 3.5                             | Layered WCET Analysis                                                                                                                                                                                         | 42                                   |

|          | 3.6                             | Splitting a Program                                                                                                                                                                                           | 43                                   |

|          | 3.7                             | Processor-Behavior Analysis                                                                                                                                                                                   | 46                                   |

|          | 3.8                             | Control-Flow Analysis                                                                                                                                                                                         | 47                                   |

|          | 3.9                             | Estimate Calculation                                                                                                                                                                                          | 50                                   |

|          | 3.10                            | Path-based Estimate Calculation                                                                                                                                                                               | 52                                   |

|          |                                 | Tree-based Estimate Calculation                                                                                                                                                                               | 52                                   |

|          | 3.12                            | The Implicit Path-Enumeration Technique (IPET)                                                                                                                                                                | 56                                   |

|          | 3.13                            | The Measurement-based Approach                                                                                                                                                                                | 62                                   |

|          | 3.14                            | Input Data Generation                                                                                                                                                                                         | 65                                   |

|          | 3.15                            | Measurement                                                                                                                                                                                                   | 67                                   |

#### Contents

|               | 3.16                                                               | Chapter Summary                                                                                                                                                                                                                                             | 70                               |

|---------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 4             | Red<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | Chapter Summary  ucing Pessimism  Pessimism  Monotonicity  State as an Encoding of History  Context-sensitive IPET  Contexts  Context Constraints  Timed Traces and Clips  Finding Contexts for MBTA  Instantiating Context-Sensitive IPET  Chapter Summary | 77 78 78 80 80 85 99 109 112 119 |

| 5             |                                                                    | ucing Optimism  Measurements and Optimism  FROO                                                                                                                                                                                                             | 123<br>124<br>126<br>129<br>131  |

| 6             | FOH<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                             | RTAS: High-Precision MBTA  Requirements                                                                                                                                                                                                                     | 138<br>139<br>141                |

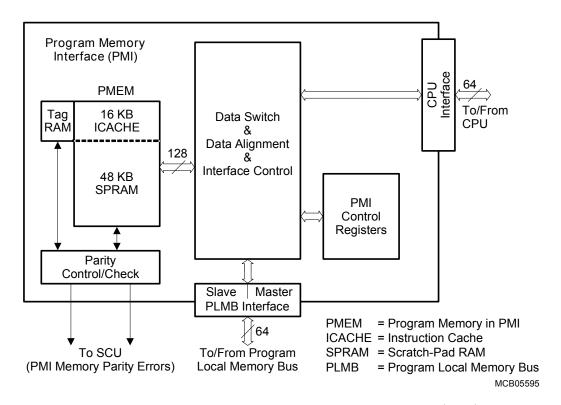

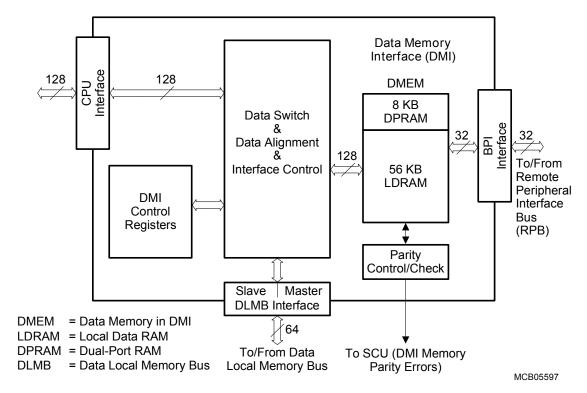

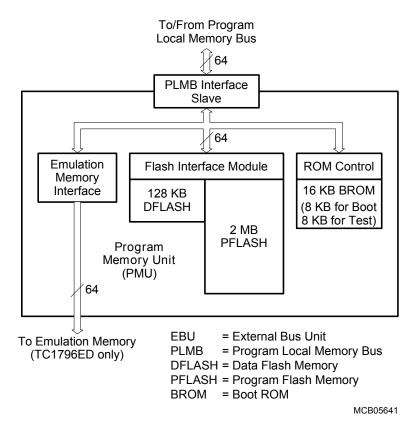

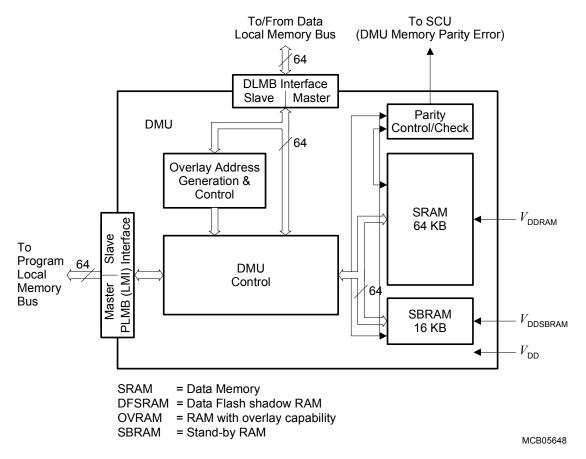

| 7             | Exp<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7               | eriments The TriCore TC1796                                                                                                                                                                                                                                 | 151<br>153<br>154<br>155<br>156  |

| 8             | Con<br>8.1<br>8.2                                                  | Conclusion and Outlook  Conclusion                                                                                                                                                                                                                          |                                  |

| $\mathbf{Bi}$ | bliog                                                              | graphy                                                                                                                                                                                                                                                      | 189                              |

| Lis           | st of                                                              | Figures                                                                                                                                                                                                                                                     | 211                              |

| Lis           | st of                                                              | Tables                                                                                                                                                                                                                                                      | 213                              |

| Image Sources | 215 |

|---------------|-----|

Contents

$\begin{tabular}{ll} A pessimist sees the difficulty in every opportunity; an optimist sees the opportunity in every difficulty. & -Winston Churchill \\ \end{tabular}$

CHAPTER 1

# Thesis Overview

In this introductory chapter, we provide an overview of the topic and the contributions of this thesis.

We consider the need for close estimates of the worst-case execution time of soft-ware tasks during the construction of a real-time computer system. We contrast the traditional methods used for worst-case execution time estimation to the relatively new measurement-based approach. We present multiple use-cases for the measurement-based approach, where it seems favorable over traditional methods. We mention the problematic effects of optimism and pessimism, which are associated with the measurement-based approach. We then point out the contributions of this thesis and close the chapter by giving an outline of the rest of the text.

#### 1.1 What is the WCET?

The worst-case execution time (WCET) of a given program on a particular execution platform is the maximal amount of time the program may require to execute, from the moment it is started to the moment it completes its execution.

## 1.2 Why do we need WCET Estimates?

A real-time computer system is a computer system in which the correctness of the system behavior depends not only on the logic results of the computations, but also on the physical instant at which these results are produced [Kop97].

Today, most real-time computer systems are implemented as collections of software tasks that are executed concurrently on a suitable hardware platform consisting of one or multiple microprocessors or microprocessor cores. Obtaining the WCET of all real-time tasks is an essential step in ensuring the correctness of such a system.

In the field of WCET analysis, we consider the problem of obtaining the WCET of a given task running on a particular hardware platform [WEE<sup>+</sup>08]. It turns out that obtaining the exact WCET is infeasible in most practically relevant cases, due to the large number of possible behaviors that even a moderately complex piece of software can

exhibit on modern computer hardware. As a consequence, a major research focus of the WCET community is the development of methods for inferring WCET estimates.

For practical use, the WCET estimates must be *close*, i.e., they should be as close to the actual WCET as practically feasible.

The WCET of a given task is always specific to its particular executable machine code, as well as to the target hardware on which that code is executed. There is no general method that could be used to obtain the WCET, or even a reasonably close estimate thereof, of arbitrary code to be run on an arbitrary microprocessor.

#### 1.3 Traditional Methods for WCET Estimation

The most straightforward way to obtain an estimate for the WCET of a given piece of code on a particular target platform is to observe the end-to-end execution times while that piece of code is executed under different execution scenarios, to pick the maximal observed execution time, and to multiply that value with a safety factor that is specific to the intended application. This is what is partly done in industry in the case of low-criticality systems under the term *dynamic timing analysis* [WEE<sup>+</sup>08]. However, the same approach cannot be used for safety-critical systems.

Unlike in other fields of engineering, like, for example, construction, where systems usually demonstrate mostly continuous behavior that is suitable for such forms of extrapolation, it turns out that digital systems typically demonstrate many behavioral discontinuities. As a result, the actual WCET cannot easily be extrapolated from a set of observed execution times. Situation can and do occur, where the WCET is only triggered in rare situations that cannot be adequately modeled by continuous mathematical models. For critical applications, however, such rare situations must be considered, to ensure correct, dependable, and safe operation.

The traditional approach for WCET analysis is *static timing analysis*, where a WCET estimate is calculated directly from the executable machine code. Analysis methods that follow this approach depend on a correct and precise behavioral model of the target hardware on which the code is intended to be executed. As a result, such methods are highly dependent on the intended target hardware.

Developing a static WCET analysis for a modern microprocessor is an expensive and error-prone undertaking, as such hardware usually contains an abundance of performance optimization features, like caches, buffers, processor pipelines, branch predictors, etc. Due to the intricate interaction of these features, static analysis methods are forced to make simplifying assumptions during WCET inference, which can lead to considerably imprecise WCET estimates.

## 1.4 Measurement-based Timing Analysis (MBTA)

Measurement-based timing analysis (MBTA) methods [BCP02, BCP03, KWRP05, WKRP09, SM10] try to alleviate the portability issue of static timing analysis. MBTA is an easily retargetable analysis approach for estimating the WCET of a given task running on a particular target platform. In MBTA,

- 1. the execution times of individual task fragments are measured while the task is being executed on the target hardware, and

- 2. the observed local execution times of the individual task fragments are subsequently combined into a global WCET estimate for the task as a whole.

A major strength of MBTA is its low retargeting effort. Retargeting requires the implementation of a target-specific driver that compiles and links the code of the task, uploads the executable machine code to the target platform, starts the execution of the code, and records the execution time of individual program parts.

Because the space of possible input data is usually enormous, it is not feasible to perform individual measurements on all possible input configurations. A subset of possible input data must be chosen. As a result, MBTA methods face the challenge of *optimism*: A WCET estimate obtained using MBTA may be lower than the actual WCET. This is very different from the situation in static analysis, which is always conservative in its assumptions about worst-case behavior, even at the cost of a potentially high overestimation of the actual WCET. A WCET estimate obtained from a correct static WCET analysis is a guaranteed upper bound of the actual WCET.

Consequently, the subset of input data on which measurements are carried out must be selected carefully. Generating suitable input data, in order to limit the extent of underestimation, is therefore a crucial issue in MBTA.

#### 1.5 Use Cases for MBTA

The properties mentioned in the previous section make MBTA suitable for the following scenarios:

Development of soft real-time systems: A soft real-time computer system is being developed, where an occasional miss of a task completion deadline can be tolerated. MBTA is particularly expedient for systems with high resource utilization, where close WCET estimates are particularly important.

Development of mixed-criticality systems: A mixed-criticality computer system [BLS10] is being developed. For such a system, it is possible to use a mix of static timing analysis and MBTA. In such a mixed analysis approach, static timing analysis can be used to obtain WCET estimates associated with a high criticality level, whereas MBTA can be used to obtain WCET estimates associated with a low criticality level. Dynamic mixed-criticality scheduling algorithms [BBD+10, BLS10, BBD11] can then be used to guarantee that all highly critical task are timely scheduled.

Testing and evaluation of static WCET tools: A new static WCET analysis is being developed in-house, for example, because there is a need to analyze a hard real-time system, but no suitable analysis tool is available for the chosen target hardware. MBTA can then be used to test and evaluate the newly developed static analysis tool.

Cross-checking of analysis results: A static WCET analysis tool from a third party vendor is used to analyze a highly critical hard real-time system. MBTA can be used to cross-check the obtained WCET estimates.

Development of gracefully-degrading real-time systems: A hard real-time computer system is being developed, but the costs for developing a static WCET analysis is prohibitive. MBTA can then be used to obtain WCET estimates. These estimates can be used for scheduling, under the condition that the system provides a suitable safe fall-back operation mode, which is guaranteed to be entered automatically in the unlikely case of a timing error.

**Design space exploration:** A hard or soft real-time computer system is being developed, but there are still open design decisions. At this stage of development, MBTA can be used for design space exploration, to help the system designer in evaluating different choices of target hardware, algorithms, task factorization, etc.

#### 1.6 Optimism and Pessimism

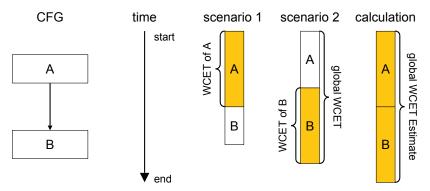

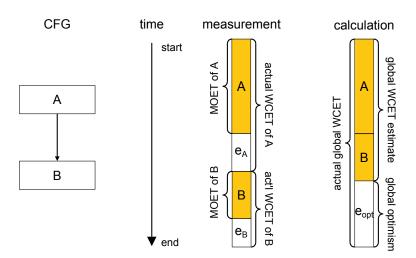

In MBTA, the program code under analysis is executed on the target hardware, and the execution times for different program parts are observed. In the simplest case, the considered parts are individual instructions or non-overlapping code blocks [BCP02, BCP03, WKRP09]. Another possibility is to consider individual instruction sequences occurring in the code [BCP02, BCP03]. Typically, the maximal observed execution times (MOET) of each program part is then taken as approximation of the block's WCET. A global WCET estimate for the whole task can then be computed by combining the local MOETs.

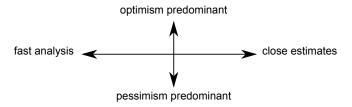

A crucial issue in MBTA is closeness. The quality of the WCET estimate is determined by the ability to control two diametrically opposed sources of deviations:

Pessimism: When inferring a global WCET estimate, we combine the local WCET estimates of the individual program parts in a conservative fashion, i.e., we assume that the effects that lead to local WCETs of individual program parts may accumulate during program execution, even if we have not witnessed such a situation during measurement. The rationale for choosing this form of over-approximation is that the WCET is, by definition, a pessimistic parameter of a task. Unless we have collected sufficient evidence to the contrary, we assume the existence of execution scenarios where local WCETs of different program parts accumulate. On a global level, this form of abstraction can lead to a potential overestimation of the actual WCET.

Assume, for a moment, that we knew the actual WCET of each program part. In this case, any monotonic composition method for calculating a global WCET estimate introduces some error  $e_{pess} \geq 0$ , such that we have  $\widehat{est} = wcet + e_{pess}$ , where  $\widehat{est}$  is the *optimism-free* global WCET estimate, and where wcet is the actual global WCET.

**Optimism:** In MBTA, we cannot be sure that our measurements capture all possible execution times of a given program part, for the following two reasons:

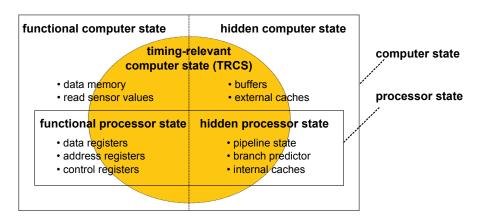

- The size of the relevant state space, i.e., the space of possible initial conditions with respect to the *timing-relevant computer state* (cf. Section 3.3) is usually prohibitively large.

- We want MBTA to be portable, so we do not want to tailor the method to the specifics of any particular target hardware.

Although MBTA applies sophisticated input-data generation techniques to achieve measurements that cover most of the possible temporal behaviors of the individual task parts, it cannot guarantee that the local MOET, on which the global WCET estimate is based, hits the local WCET. Globally, this effect can lead to a potential underestimation of the actual WCET of the task as a whole.

Unlike static WCET analysis, MBTA intentionally does not consider the implementation details of the processing hardware, in order to preserve the portability of the method. Also, checking all possible execution times of a given code block exhaustively by enumeration is not feasible in practice, due to the size of the initial state space. As a consequence, taking the MOET of each block as an estimate of the block's WCET is inherently optimistic. Assuming, again, that a monotonic composition method is used to calculate the global WCET estimate, optimism introduces an additional error  $e_{opt} \geq 0$ , such that  $est = \widehat{est} - e_{opt} = wcet + (e_{pess} - e_{opt})$ , for the WCET estimate est under a combination of optimism—introduced by relying on measurements—and pessimism—introduced by relying on overapproximative estimate calculation.

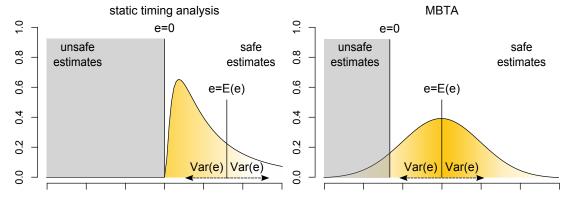

Figure 1.1: The closeness of a WCET analysis method can be quantified by reference to the variance Var(e) and the estimated value E(e) of the estimation error e = est - wcet. In the case of static analysis, the area of unsafe estimates is excluded by using overapproximation, and closeness quantifies the expected overestimation. MBTA, however, does not guarantee safety. In this case, estimates might be higher or lower than the actual WCET, and closeness quantifies the expected deviation from the actual WCET. To increase the closeness of MBTA, we must reduce both, the variance Var(e) of the WCET estimate's error and the deviation wcet - E(e) of the expected value of the WCET estimate's error from the actual WCET. Note that Var(e) and wcet - E(e) correspond to the notions of accuracy and precision in metrology, respectively.

One way to quantify the closeness of an analysis method is by reference to the variance Var(e) and the expected value E(e) of the estimation error e = est - wcet, as illustrated by Figure 1.1. To increase the closeness of MBTA, we must reduce both, the variance Var(e) of the WCET estimate's error and the deviation wcet - E(e) of the expected value of the WCET estimate's error from the actual WCET. This can be achieved by reducing pessimism and optimism simultaneously.

#### 1.7 Contributions

A major requirement for a good MBTA tool that is in industrial practice is that it should be able to produce close WCET estimates, i.e., estimates that are as close to the actual WCET as practically feasible. To achieve this, the analysis must limit the influence of both, optimism and pessimism. Moreover, such a practical tool should be easy to deploy and use.

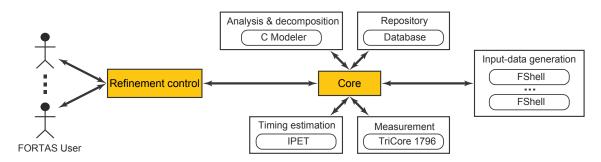

In this thesis, I condense and extend research results that have been obtained within the FORTAS project. The goal of the FORTAS project was foundational research into new methods for MBTA, which should pave the way for the development of industrial-strength MBTA tools. Central research topics that were treated within the FORTAS project are new strategies for reducing both, pessimism and optimism, and the iterative refinement of analysis results. On a higher level, the FORTAS approach aims at tying together all these methods into an integral analysis approach.

Various individual results from the FORTAS project have been published in prior scientific publications [BT08, ZBK09, ZBK10, BZTK11, BZK11, ZBK11, vHHL<sup>+</sup>11]. In this thesis I strengthen the following original contributions<sup>1</sup>:

**Context-sensitive IPET:** In Section 4, I discuss context-sensitive IPET as a strategy for reducing the pessimism found in standard IPET.

**Integration of methods:** In Chapter 6, I discuss how the methods for reducing optimism and pessimism that have been developed within the FORTAS project have been tied together to form a complete MBTA approach that can provide closer WCET estimates than possible with standard MBTA approaches.

**Experimental results:** In Chapter 7, I present an experimental evaluation of the FORTAS approach. The results indicate the effectiveness of the approach. Most importantly, the evaluation includes a quantitative comparison between analysis results obtained by the FORTAS tool and the corresponding results of the industrial-strength static WCET analysis tool AIT.

#### 1.8 Guide to this Thesis

Chapter 2—Real-Time Computer Systems: In this chapter, we review the basic concepts of real-time computing. In Section 2.1, we start with the definition of

<sup>&</sup>lt;sup>1</sup>Notice: The results presented in Chapter 5 have mostly been obtained through the research effort of Sven Bünte, as part of our research collaboration within the FORTAS project. The author of this thesis provides this overview for the sake of completeness, but does not claim any scientific results in that chapter as his own.

a real-time system. In Section 2.2, we discuss available design options for real-time computer systems. In Section 2.3, we take a look at the development process of critical systems. In Section 2.4, we review the concept of a task. We then review task scheduling on uniprocessors, in Section 2.5, and on multiprocessors, in Section 2.6.

Chapter 3—Introduction to WCET Analysis: This chapter presents the preliminaries of WCET analysis. After considering several simplifying restrictions on the hardware and software under analysis that are usually assumed for WCET analysis (cf. Section 3.1), we discuss the influence of modern high-performance microarchitectures on WCET analysis in Section 3.2. In Section 3.3, we consider what parts make up a computer's state, and how these parts may affect the temporal behavior of a running program. We then consider the software development process in Section 3.4, and its implication on WCET analysis in Section 3.5. The traditional approach for WCET analysis follows the idea of splitting the program under analysis into smaller parts and determining local WCET estimates for these individual parts. In Section 3.6 we discuss different splitting choices. Processor-behavior analysis, which we discuss in Section 3.7, is concerned with determining WCET estimates for the individual program parts. Control-Flow Analysis, which is discussed in Section 3.8, is concerned with determining the feasible sequences in which the individual program parts can be executed. Estimate calculation, which is concerned with combining the local WCET estimates obtained by processor-behavior analysis into a global WCET estimate for the whole program, is discussed in Section 3.9. We then discuss concrete methods for WCET estimate calculation, in Sections 3.10, 3.11, and 3.12. In Section 3.13, we discuss the general principles of MBTA. In Section 3.14, we discuss the MBTA issue of generating suitable input data. We conclude the chapter with a discussion of measurement, in Section 3.15.

Chapter 4—Reducing Pessimism: In this chapter, we develop a method for reducing pessimism in MBTA. In Section 4.1, we consider how pessimism arises due to overapproximation of the systems behavior. In Section 4.2, we consider a particular property found in many widely used estimate calculation methods that we need later to ensure our method for reducing pessimism can never increase pessimism. In Section 4.3, we consider that the state of a system can be viewed as a summary of its execution history, which allows us to obtain partial state information from execution histories. In Section 4.4, we present context-sensitive IPET, a generic estimate calculation method. In Sections 4.5 through 4.9, we present a concrete instantiation of context-sensitive IPET that is suitable for practical applications.

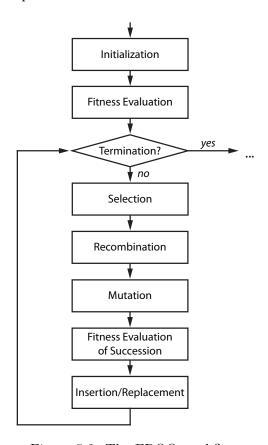

Chapter 5—Reducing Optimism: In this Chapter, we describe a method for reducing optimism in MBTA. In Section 5.1, we identify measurements as source of optimism in MBTA. In Section 5.2, we present FROO, an input-data generation technique that seeks to reduce the optimism of MBTA through an increase of the measurement coverage of temporal behavior. In Section 5.3, we present an evaluation for FROO. In Section 5.4, we describe some limitations of FROO.

Chapter 6—FORTAS: In this chapter, we present the FORTAS approach for highprecision MBTA. In Section 6.2, we review the features that distinguish the FOR-

#### 1. Thesis Overview

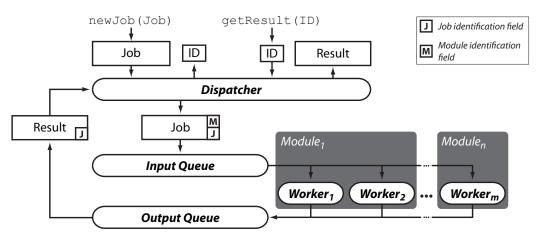

TAS approach from standard MBTA methods. One particularly innovative feature is iterative refinement, which we review in Section 6.3. In Section 6.4, we review the modular software architecture of the FORTAS tool.

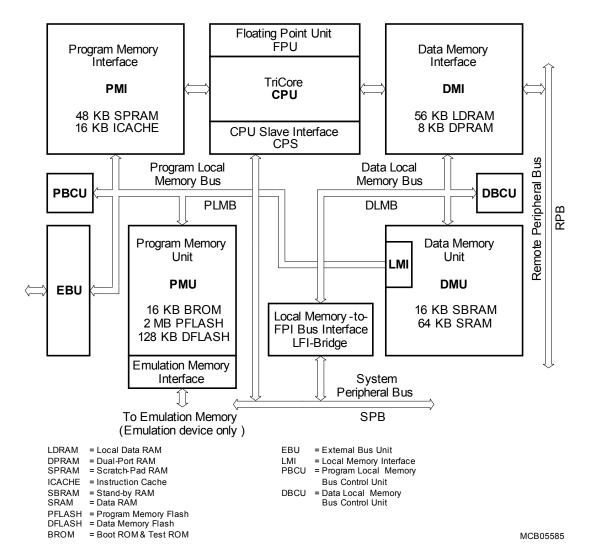

Chapter 7—Experiments: In this chapter, we present an experimental evaluation of the FORTAS approach. We first describe the target platform that we used in our evaluation. In Section 7.1, we present the TriCore TC1796 microprocessor. In Section 7.2, we present the OCDS debugging interface, which provides the technical prerequisites for collecting timed execution traces without exerting a probe effect on the system. In Section 7.3, we present the TriBoard TC179X Evaluation Board that we used as a platform for the TC1796. In Section 7.4, we present the benchmarks that we used. In Section 7.5, we explain the design of our experiments. In Section 7.6, we present the results of our evaluation.

Chapter 8—Conclusion and Outlook: This chapter closes the thesis, with the conclusion formulated in Section 8.1, and an outlook to future research in Section 8.2.

# Real-time Computer Systems

In this chapter, we review the basic concepts of real-time computing.

A real-time system is a computer system in which the correctness of the system behavior depends not only on the logic results of the computation, but also on the physical instant at which these results are produced.

In Section 2.1, we start with the definition of a real-time system. We point out the fundamental difference between *hard* and *soft* real-time systems. We also review the related concepts of *safety-critical computer systems*, *mission-critical computer systems*, *mixed-criticality computer systems*, *cyber-physical systems*, and *hybrid systems*.

Next, we consider design and development of real-time systems. In Section 2.2, we discuss available design options for real-time computer systems. In Section 2.3, we take a look at the development process of critical systems.

We then consider multi-tasking in real-time systems. In Section 2.4, we review the concept of a task, which is the fundamental building block of a modular real-time system. We then review task scheduling on uniprocessors, in Section 2.5, and on multiprocessors, in Section 2.6. We review some classic *schedulability tests*—analytic criteria that traditionally form the basis for ensuring the correctness of a multi-tasking real-time system. These tests require knowledge of the WCET—or at least a WCET estimate—of each task. Schedulability analysis is thus a primary motivation for WCET estimation.

## 2.1 What is a Real-Time Computer System?

A real-time computer system is a computer system in which the correctness of the system behavior depends not only on the logic results of the computations, but also on the physical instant at which these results are produced [Kop97].

Real-time computer systems typically manifest themselves in the physical world as *embedded computer systems*, i.e., special-purpose computer systems based on application-specific hardware and software, often implemented as a self-contained physical device. Typical applications of embedded computer systems include mobile phones, video game consoles, media players, electronic control units in various kinds of ground, air, naval, and space vehicles, plant automation systems, and medical devices. Figure 2.1 shows some typical applications of real-time computer systems.

Figure 2.1: A few application examples of real-time computer systems: (a) DVD player, (b) capsule endoscope, (c) GPS satellite, (d) laproscopic surgery robot, (e) civil airplane, (f) industrial laser cutter, (g) planetary rover, (h) remotely operated underwater vehicle, (i) unmanned aerial vehicle.

Most embedded computer systems interact tightly with their physical environment. As a consequence, they are usually subject to *real-time constraints* that are imposed by the real-world objects that they interact with.

For some applications, the imposed real-time constraints are more rigid than for others. For example, an embedded controller for the combustion engine of a car must be able to inject the correct amount of fuel into the combustion chamber precisely at the right instant in time when the piston in the cylinder reaches the right position. A failure in timing can severely impact the efficiency of the engine, or even cause physical damage to the point where the safe operation of the car is compromised [Kop97]. In avionics, flight control software must execute within a fixed time interval in order to accurately control the aircraft [DB11]. Temporal constraints of this kind are called hard real-time constraints, and computer systems that are subject to at least one hard real-time constraint are called a hard real-time computer systems [Kop97].

On the other hand, there are also many embedded systems that, while still classified as real-time, are subject to less rigid timing constraints. A typical example are media players, where a voluminous stream of data needs to be processed in real time, but where an occasional miss of a temporal deadline can be tolerated, as it would merely lead to a degradation in service quality. For example, the dropping of a single frame from a video stream due to resource overload is hardly noticeable to the human viewer. However, if too many frames are dropped, the service quality of the system is impeded to a point where the system would be considered unusable. Temporal constraints of this kind are called soft real-time constraints, and computer systems that are subject to

at least one soft real-time constraint—but no hard real-time constraint—are called *soft* real-time computer systems [Kop97].

Occasionally, a further distinction is made between hard real-time computer systems and firm real-time computer systems, in which case a hard real-time computer system is defined as a system where a failure in the temporal domain can lead to a catastrophe, whereas in a firm real-time computer system this is never the case [Kop97].

A computer system that must operate correctly to ensure the safety of people and the environment is called a *safety-critical computer systems* [Sto96, Kni02]. Any hard real-time computer system is therefore, by definition, also a safety-critical computer system. On the other hand, a *mission-critical computer system* is a computer system where a failure can degrade or prevent the successful completion of an intended operation [Fow04]. An example of a mission-critical computer system would be an electronic trading system. In the special case of algorithmic trading [KK07b], these systems also classify as soft real-time systems.

An example of a safety-critical system is the flight control system of an unmanned aerial vehicle (UAV). A malfunction of this system may cause the vehicle to crash and cause direct damage to people and the environment. On the other hand, the navigation system might be considered less critical. A failure of this system may cause the vehicle to fail on its mission, but—in the case of a carefully designed system—it will still be possible to control the vehicle and safely abort the mission.

A mixed-criticality computer system is a safety-critical computer system that contains one or more parts that are considered non-critical, or less critical than the other parts of the system [BLS10]. Coming back to the previous example, the UAV's control system is a mixed-criticality system, if the flight control and navigation are integrated into a single system.

We use the more general term *critical systems* to refer to the union of safety critical and mission-critical systems. Since a mixed-criticality system is a special kind of safety-critical system, it follows that a mixed-criticality system is also a critical system, but, on the other hand, not every critical system needs to be a mixed-criticality system.

Rather recently, the term *cyber systems* has been coined to designate systems that perform computational tasks—in particular digital computer systems. This contrasts *physical systems*, which involve the transformation of matter and energy. Such systems subsume, for example, mechanical, chemical, or biological systems.

Accordingly, the term *cyber-physical system* designates a system that combine physical and cyber components, where the cyber components are usually embedded computer systems. Since these cyber components typically need to interact with the physical components in timely manner, a cyber-physical system is usually a real-time system. Moreover, networked communication is frequently considered as a salient ingredient of a cyber-physical system. The theory of cyber-physical systems views such systems as an integrated whole, providing tools and techniques for modeling, designing, and analyzing them.

Physical systems are characterized by their apparent *continuous dynamics*, which can be modeled by continuous mathematics. On the other hand, cyber systems—which are usually implemented using digital computer hardware—are characterized by *discrete dynamics*, which can be modeled by discrete mathematics. Systems that exhibit both, continuous and discrete dynamics, are known as *hybrid systems*.

#### 2.2 Design Options

Most real-time computing systems are implemented on special-purpose embedded hardware that is suited to their application-specific resource requirements. There are three basic options for realizing the computational part of a real-time computing system. In practice, systems may be designed using a mix of these options:

Hardware Solution The first option is to implement the computational functionality completely in application-specific hardware. The result is an ASIC that is subsequently produced by a semiconductor manufacturer. Such application-specific hardware can be highly optimized to perform application-specific tasks effectively. However, once the ASIC has been produced, its design cannot be modified any more, which rules out any adjustments that might turn out necessary or beneficial at a later time. Moreover, the production of an ASIC is usually only cost-effective in high volumes.

Software Solution At the other end of the hardware/software spectrum, the computational functionality can be implemented in software running on an off-the-shelf embedded microprocessor. Typical microprocessor families that are found in embedded devices are the MPC5500 processor series from Freescale Semiconductors, the ARM processor series from ARM Ltd., the TriCore processor series from Infineon Technologies, the AVR processor series from Atmel Corporation, and the Cortex processor series from NXP Semiconductors, to name only a few common examples.

Reconfigurable Hardware Solution The third option is to use a FPGA. These programmable devices offer the flexibility of an ASIC in the sense that they allow for the implementation of arbitrary, user-defined logic functions. This flexibility includes the possibility of implementing complete soft-core processors [TAK06]. Unlike an ASIC, an FPGA can be reprogrammed, allowing for design modifications long after the system has been manufactured, for example as a part of routine system maintenance. Taking advantage of this technology, reconfigurable instruction set processors [BL00], for example, are able to dynamically adapt their instruction set to the application being executed. More generally, reconfigurable computing [Bob07] embraces the idea of routinely changing the hardware design at runtime. A computer system that implements the idea of reconfigurable computing can, for example, dynamically add special-purpose processing components as they are needed.

Identifying a balanced design that combines the benefits of these three basic solutions is a fundamental problem that is addressed in the discipline of *hardware/software co-design*.

In this thesis, we are concerned with analyzing the execution time of individual pieces of software running on a microprocessor, i.e., we are dealing with systems that have been designed according to the second design option. Methods for execution-time analysis of hardware, which are needed in the case of a hardware solution, are, for example, presented in [BC09]. Concerning reconfigurable hardware, some preliminary ideas have been presented in [KBZ10].

#### 2.3 Dependability and the Development Process

Many real-time systems perform critical tasks during their interaction with the physical world. Consequently, such systems are usually subject to various kinds of *dependability* requirements.

Besides dependability requirements like reliability, maintainability, and availability of the system, one of the most critical requirements is usually safety, meaning that the system must not exert damage to people or the environment. Systems like flight-control systems, traffic-signaling systems, control systems for nuclear power plants, and many medical systems are considered to be highly safety-critical.

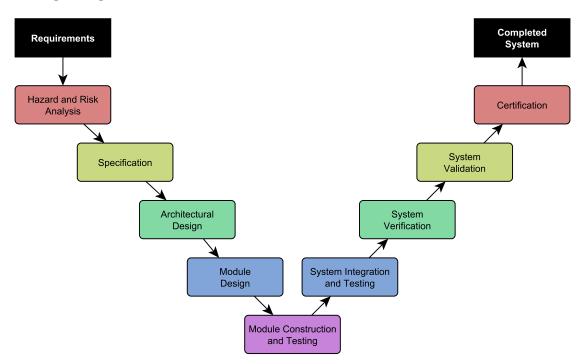

To ensure that a critical system is safe, the developers must follow a rigid design process that includes planning, implementation, review, and reporting [BP82, Fow04]. One of the most widely used development life-cycle models for the design of critical systems is the V-model [STA89, Sto96]. This model depicts the major processes involved in the design of a critical system, as well as the primary flow of information between these processes. Figure 2.2 shows a generic version of the model, as presented in [Sto96].

The information flow can be interpreted to indicate a natural sequencing of individual development phases, although, in practice, the development does not need to be strictly linear. For example, it is possible to make use of pipelining techniques to speed up the development process.

Figure 2.2: The V-model is a typical development life-cycle model that is applicable for the design of critical systems. It depicts the major processes in the development, as well as the primary flow of information between them. This particular version of the model is adopted from [Sto96].

As indicated in the model, critical systems must typically receive approval by an

official, independent certification agency. During the certification process, the manufacturer of the system is obliged to convincingly demonstrate the safety of his system. Because timing errors can affect the correct behavior of a real-time system, demonstrating temporal correctness is an important issue during certification.

Besides safety, another dependability requirement that has recently gained increasing importance in embedded and real-time computing is security. Today, more and more systems use shared processing resources or are interconnected via various kinds of networks. In the case of critical systems, it is vital to provide mechanisms and techniques that ensure the integrity of the system in the case of a malicious attack.

#### 2.4 The Task Abstraction

Modern real-time systems are usually highly complex artifacts. To avoid unnecessary complexity in the engineering process and to keep the systems maintainable, the software of a real-time system is hardly ever designed as a monolithic piece of code. Rather, a typical design is based on a collection of cooperating *software tasks* that together serve to provide the intended service. This simplifies the isolation and correction of errors, maintenance, and the later addition of new functionality.

According to [Kop97], a task is the execution of a sequential program that starts with reading some input and state data, and terminates with some output and an update of state data.

The execution time of a given task does not include waiting times that are caused by synchronization with other tasks. As these delays depend on the progress of other tasks, they are better addressed at the scheduling level (cf. Sections 2.5 and 2.6). For execution time analysis, it is then safe to assume that all synchronization operations complete without waiting.

On systems that allow task preemption, a given task may be interrupted during execution, and resumed at some later time. In the meantime, other tasks or operating system software may execute on the same hardware. Such a behavior is problematic for WCET analysis, because preemption can normally occur at almost arbitrary points in a task, and any code that is executed between the preemption and subsequent resumption of a task may influence its execution time through non-functional dependencies. For example, in the presence of an instruction cache, tasks may influence each other's execution time by accessing conflicting addresses.

Depending on the application, a real-time system can be subject to different kinds of temporal constraints. Most commonly, the system is expected to deliver a certain service within a specified interval of time, i.e., at a given reference point in time t, the system must deliver its service within a maximal response time RESP. To do so, all the corresponding tasks in the system that are associated with the particular service must complete within the allowed time interval [t, t + RESP].

## 2.5 Task Scheduling on Uniprocessors

In a multi-tasking real-time system there are multiple tasks—subject to different timing constraints—that need to be executed in a concurrent fashion. To coordinate the arising competition for processing resources, there is a need for an execution *schedule*, a plan

that determines at what times each task is to be executed on which processing unit, such that all tasks can finish execution on time. Such a schedule can be created either statically before the system is started, or dynamically during system execution:

- In *static scheduling* the temporal assignment of tasks to processing units is performed before the system is started, usually at the time when the system is designed.

- In *dynamic scheduling* a software scheduler, which executes alongside normal system tasks, decides at runtime which task should be assigned to which processing unit at any given point in time.

A static schedule is a fixed temporal assignment of tasks to processing units. This means that each task has one or more fixed time windows during which it is allowed to execute. The size of the time window(s) determines a maximal amount of time for which each task may run.

Once a WCET estimate is known for all tasks, it becomes possible to check whether a given static schedule allows each task to successively complete its purpose. If that is not the case, knowledge of the WCET estimates allows the system designer to redesign the schedule, such that all task deadlines can be met.

Concerning dynamic scheduling, there exists an abundance of different strategies for real-time systems. Here we mention just four particularly popular strategies for assigning independent tasks to a single processing unit, which are: rate-monotonic scheduling (RMS) [LL73], deadline-monotonic scheduling (DMS) [ABRW91, Aud93], earliest deadline first scheduling (EDF) [XP90], and least laxity scheduling (LL) [DM89]. All four strategies base their scheduling decisions on task priorities. At run time, whenever a task completes or a new tasks becomes ready for scheduling, a pending task with maximal priority is selected and dispatched. However, the four strategies use different metrics to assign a priority to each task.

- RMS assumes that each critical task  $T_i$  becomes ready for scheduling and must be completed periodically within a fixed time period of length  $p_i$ . The priority of each task  $T_i$  is based on its period: Tasks with shorter periods receive higher priority than tasks with longer periods. The RMS strategy can easily be extended to allow for the scheduling of additional non-critical tasks by assigning them priorities below those of any critical task.

- DMS is a generalization of RMS that allows tasks with deadlines that are placed before the end of the respective task period. This enables the modeling of communication overhead and sporadic tasks [ABRW91, Aud93].

- EDF bases the priority of each task on its upcoming deadline: Tasks with shortly upcoming deadlines receive higher priority than tasks with later deadlines.

- LL scheduling—also known as *least slack time* (LST) scheduling—establishes the priority of a task based on its slack time, i.e., the difference between its remaining time budget until its deadline and its remaining execution time. By assigning higher priorities to tasks with a lower slack time, the strategy makes sure that

pending processes are deferred as long as permissible with respect to the given deadlines.

All four strategies are *optimal* for scheduling independent, i.e., non-synchronizing, preemptable tasks on single-processor systems, in the sense that they will always find some schedule that allows all critical tasks to meet their deadlines, if such a schedule exists for the given collection of tasks.

However, testing whether such a schedule exists is usually not easy. In practice, sufficient *schedulability tests* are applied to ensure that a given set of critical tasks is schedulable under all possible circumstances.

For a given collection of n tasks  $T_1, \ldots, T_n$ , the inequality

$$\sum_{i=1}^{n} \frac{wcet_i}{p_i} \le n \cdot (\sqrt[n]{2} - 1)$$

forms an utilization-based, sufficient condition for the collections schedulability under the RMS strategy [LL73]. In this inequality,  $wcet_i$  denotes the worst-case execution time (WCET) of task  $T_i$ , i.e., the maximal amount of time that  $T_i$  may take to execute, if started and left running uninterruptedly. To apply this test, it is therefore necessary to first determine the WCET of each task. Finding the WCET of a task is not at all trivial, though. In fact, determining the exact WCET of a given piece of executable code running on a particular hardware platform is usually intractable. The field of worst-case execution time analysis is concerned with providing suitable approximation techniques that can be used to obtain estimates of the WCET.

There exists a similar schedulability test for the EDF strategy [XP90]. Again, we need to know the WCET of each task, in order to apply this test:

$$\sum_{i=1}^{n} \frac{wcet_i}{p_i} \le 1.$$

Concerning the DMS strategy, Audsley et al. present an algorithmic schedulability test in [ABRW91]. Again, the test uses the WCET of all tasks.

Lastly, let's reconsider the LL scheduling strategy. To determine the priority of a given task, LL needs to determine that task's remaining execution time. The most practical—albeit conservative—way to do this is to dynamically track how much time each task has spent executing so far, and to take the difference to the tasks WCET as a pessimistic estimate of the task's remaining execution time. Again, we need to know to WCET of each task.

## 2.6 Task Scheduling on Multiprocessors and Recent Trends

The four scheduling strategies we have just seen are suitable and optimal for systems with a single execution unit. However, the advent of  $multiprocessor\ architectures^1$  on

<sup>&</sup>lt;sup>1</sup>Concerning scheduling, *multi-core* architectures are normally treated just as multiprocessor architectures. For simplicity, our use of the term multiprocessor architecture shall therefore also subsume multi-core architectures.

the embedded systems market has added a new level of complexity to scheduling: Unlike scheduling algorithms for uniprocessor architectures, algorithms for multiprocessor architectures must not only decide at what time each task should be run, but also on which processor it should be run.

Solving the latter problem, which is known as the *task allocation problem*, can be especially tricky in the case of *heterogeneous multiprocessor architectures*, where each processor might have different scheduling-relevant properties. In the case of *uniform multiprocessor architectures*, all processors are identical, but may run at different clock frequencies, leading to different possible execution times of the very same task instance. In the simplest case of a *homogeneous multiprocessor system*, all processors are identical and also run at the same clock frequency. As a result, in such systems the WCET of a given task instance is the same on all processors, which simplifies scheduling.

Scheduling algorithms for multiprocessor architectures can also be classified according to whether and when the allocation of a specific processor to a particular task is allowed to change. Whereas partitioned scheduling algorithms use a fixed assignment of tasks to processors, global scheduling algorithms may allow task-level migration, meaning that different task instances may be executed on different processors, or even job-level migration, meaning that each task instance may be dynamically moved between processors, during execution.

The choice of preemption policy—preemptive, non-preemptive, or cooperative scheduling—adds yet one more dimension to the space of different scheduling strategies for multiprocessor architectures.

A recent survey of algorithms and schedulability tests for multiprocessor architectures is given in [DB11].

Lately, scheduling theory has become an even more complex topic, through the advent of energy and thermal constraints. Energy constraints are particularly relevant for battery-powered devices, which are on a limited energy budget [SKL01]. Temperature constraints have become necessary for modern processors, where very high on-chip temperatures may occur under high processing load. To ensure the integrity of the system, it is necessary to limit the operating temperature, in order to prevent system failures that may occur due to overheating [FCWT11].

Even for the most recent task scheduling algorithms being developed, the WCET remains an essential parameter. For each critical task, the WCET must be determined, in order to guarantee that the system can always provide its critical services on time.

In the next chapter, we turn to the problem of determining the WCET of a given task on a particular hardware platform.

## 2.7 Chapter Summary

In this chapter, we have reviewed the basic concepts of real-time computing.

A real-time system is a computer system in which the correctness of the system behavior depends not only on the logic result of the computation, but also on the physical instant at which these results are produced. Whereas in a hard real-time system, failure to produce the result of some computation at the correct time may lead to disaster, the consequences of a similar failure in a soft real-time system are more benign. The requirements of temporal correctness are thus less rigid for soft real-time systems than

for hard real-time systems. This affects the rigor of the system development process, as well as the rigor of WCET estimation.

Today, there are multiple design options available for real-time systems. A common choice are designs that are based on a multi-tasking microprocessor. In this thesis, we focus on such designs.

The traditional way to ensure the temporal correctness of such systems is to perform a schedulability test. Such a test requires knowledge of the WCET—or at least a WCET estimate—of each task. The need to perform schedulability analysis is a primary motivation to investigate methods for WCET estimation.

# WCET Analysis

In this chapter, we consider methods for estimating the WCET of a given task running on a real-world system.

First we consider several simplifying restrictions on the hardware and software under analysis that are usually assumed for WCET analysis (cf. Section 3.1).

One major challenge that WCET analysis faces today are the complex microarchitectural features of today's high-performance microprocessors (cf. Section 3.2), which introduce a considerable jitter in the execution time of individual instructions. This jitter eventually depends on the computer state (cf. Section 3.3).

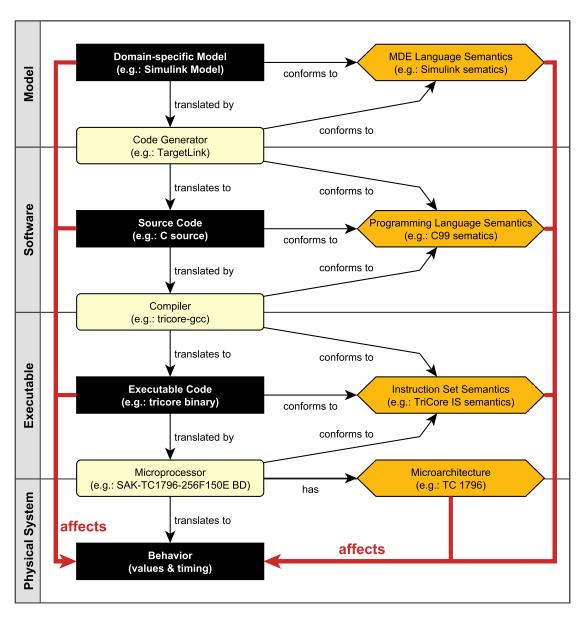

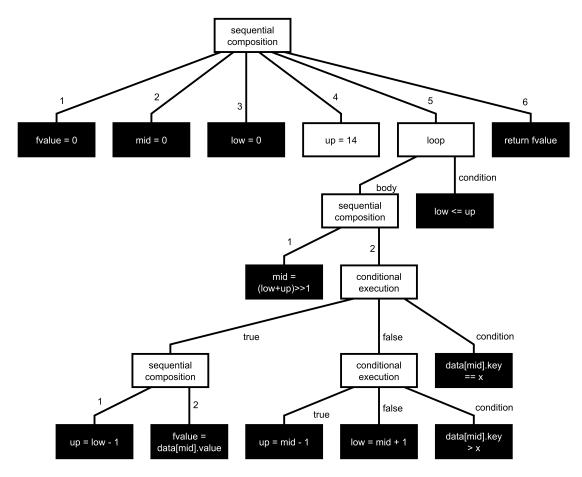

To understand the way timing analysis is implemented today, it is important to consider the software development process for real-time systems (cf. Section 3.4), which has contributed to the typical layered WCET analysis approach (cf. Section 3.5): WCET analysis is traditionally based on the idea of splitting the program under analysis into smaller parts (cf. Section 3.6), determining WCET estimates for these individual parts (cf. Section 3.7), and combining these local estimates into a global WCET estimate for the whole program (cf. Sections 3.8 and 3.9). The last combination step can be performed using different techniques, of which we discuss path-based estimate calculation (cf. Section 3.10), tree-based estimate calculation (cf. Section 3.11), and the implicit path-enumeration technique (cf. Section 3.12).

Lastly, we turn our attention to the relatively new approach of measurement-based timing analysis (MBTA) (cf. Section 3.13). The two major concerns in MBTA are the generation of suitable input data (cf. Section 3.14), and recording the execution time of individual program parts by performing measurements on the actual target hardware (cf. Section 3.15).

## 3.1 WCET Analysis of Real Software

In scheduling theory, a task is usually viewed as an abstract process that, when active, consumes processing time in a continuous way. In a real microprocessor-based system, however, a task is defined as a program that is intended for execution by one of the system's processors. The program consists of a collection of discrete instructions that are loaded into the system's instruction memory, from where they can be fetched and

processed by the processor. There are some options in microprocessors design that fundamentally affect WCET analysis:

Synchronicity: Most of today's microprocessors are implemented in synchronous logic. This means that the progress of the microprocessor's operation is controlled by a global system clock. At the beginning of each clock cycle, which is typically marked by a rising edge of the system clock signal, all the processor's latches obtain a new value that remains stable until the beginning of the subsequent clock cycle. However, the assumption of a single global clock is not valid for processors with asynchronous logic. A prominent example are microprocessors with globally asynchronous locally synchronous (GALS) logic [KGGV07]. Such a processor is driven by multiple clocks that govern individual subsystems. We are not aware of any previous work on WCET analysis of software running on asynchronous microprocessors, and we are ourselves considering synchronous microprocessor designs only. As asynchronous designs are becoming more widely used nowadays, performing WCET analysis for such microprocessors should be considered an interesting research issue.

**Determinism:** Most microprocessors designs are *deterministic*. Given the current state and all future inputs, there is exactly one possible future behavior that the microprocessor may exhibit. Still, *non-deterministic* microprocessors have been proposed for special applications [MMS01]. As with asynchronicity, we are not aware of any previous work on WCET analysis for non-deterministic processors, and we consider WCET analysis for deterministic designs.

Instruction set constancy: Some modern microprocessor provide multiple instruction sets that may be switched between dynamically. This is not only true for modern desktop and server processors, but also for certain processors that are specifically targeted at the embedded market. A good example is the ARM7 TDMI microprocessor, which features two instruction sets: The regular A32 instruction set provides a full range of unrestricted 32-bit instructions, whereas the Thumb instruction set implements a subset of restricted variants of A32 instructions, using compact 16-bit wide opcodes. As an intended use-case, an application that is running on a device with little memory may implement most functions using the Thumb instruction set, while switching dynamically to A32 for calculation-intensive code. In the present work, we consider WCET analysis for a fixed instruction set.

Frequency constancy: In traditional microprocessor designs, the global system clock runs at a fixed frequency. However, many modern power-aware designs employ dynamic frequency scaling and dynamic voltage scaling to reduce energy consumption [SKL01]. Both techniques usually imply an adaptive frequency change of the global system clock. Only little previous work is available on WCET analysis for systems with a dynamically changing clock frequency. We consider WCET analysis for a fixed clock frequency.

The assumption of frequency constancy is important for many WCET analysis methods, because it allows the calculation of the WCET from the worst-case execution cycles (WCEC), the maximum number of clock cycles that a given program requires to

execute, from the moment it is started, to the moment it completes its execution. The WCET can then be easily calculated by using the equation

$$wcet = wcec \cdot f_{clk}, \tag{3.1}$$

where  $f_{clk}$  is the microprocessor's constant clock frequency.

Having considered the effect of different hardware options on WCET analysis, we must also consider certain properties of the tasks that we are going to analyze:

**Preemption:** When a task is preempted, its is put into *ready* state, where it does not consume any processing resources. Later, it is put back into *running* state, and execution continues. During preemption, the state of the task is preserved, so that execution can later continue with the state before the task was preempted. When we consider the WCET of a preemptable task, we refer to the maximal time for which the task is actually executing, i.e., the duration of time for which it is in its *running* state.

Synchronization: Task synchronization means that two or more executing tasks together perform some joint action. This implies that all involved tasks must be ready for the joint action at the same time. If some task becomes ready for the joint action before some of the other tasks invoked, it must wait until they are also ready. Consequently, any synchronization action involves a potential delay in the execution that depends on the execution of one or more other tasks. The execution time of a given task does not include waiting times that are caused by synchronization with other tasks. As these delays depend on the progress of other tasks, they are better addressed at the scheduling level (cf. Sections 2.5 and 2.6).

**Termination:** Real-time scheduling requires a bound for the processing time of each task, i.e., it requires the task's WCET. This implies that any implementation of some task must necessarily terminate on all its possible inputs, whereas non-termination is considered an error. In WCET analysis, we therefore presume the termination of any program under analysis. The development of methods and tools for checking termination is the domain of termination analysis. Recent attempts in this area include methods that are based on model checking [CGP00], and static program analysis [CPR06].

Code constancy: We assume that the code under analysis remains invariant during execution. This simplifies code analysis by excluding self-modifying code, as well as any modification of the code by the operating system.

Input: The last issue that we consider is the question when a task receives its input. There are basically two options: Firstly, we may consider tasks that dynamically receive new input while they are being processed. The second option is a task that does not receive input while it is being processed. In this case, all inputs must be encoded in the task's initial state. The task then performs a calculation, and after the program terminates the output is encoded in the termination state. In our work we consider the second option. When we talk about the input of a task, we thus mean the input that is encoded in the initial state.

#### 3.2 Microarchitectures

Traditionally, the microprocessors employed in real-time systems used to be based on rather simple microarchitectures, where the time spent on executing a particular kind of instruction—like an addition, or a branch instruction—used to be relatively stable, or even constant. As a result, many early techniques in WCET analysis relied on the simplifying assumption of a constant local WCET for individual instructions [PK89, PS93, PS97, LM97, Pus98]. Inferring a global WCET estimate for a complete task then reduced to the problem of considering the possible execution sequences of the task's instructions, and finding the one that amounts to the highest global WCET estimate. In the case of strictly sequential execution, such an estimate can be obtained as the cost-weighted sum of instruction execution counts.

WCET analysis is traditionally biased towards pessimistic estimation, i.e., it favors estimates that are upper bounds of the actual WCET, even at the cost of a high overestimation. This is a consequence of the fact that schedulability tests are usually monotonic in the WCET estimate. For example, if we take the sufficient schedulability test for the RMS scheduling strategy [LL73]

$$\sum_{i=1}^{n} \frac{wcet_i}{p_i} \le n \cdot (\sqrt[n]{2} - 1),$$

from Section 2.5 and replace the WCET values  $wcet_i$  with corresponding estimates  $\widetilde{wcet_i}$ , such that

$$wcet_i \leq \widetilde{wcet_i}$$

, for  $1 \leq i \leq n$ ,

then, by the monotonicity of the inequality, we obtain a tighter condition that can only be satisfied in cases where the original condition is also satisfied. Hence, we see that using a pessimistic WCET estimate in place of the actual WCET might make the test fail for some tasks sets that might be classified as schedulable for the actual WCET, but it will never lead to misclassification of a non-schedulable task set as schedulable.

As a result of avoiding underestimation, many proposed techniques suffer from considerable overestimation, which forces system designers of highly critical systems to either over-dimension their systems, or to provide appropriate fall-back mechanisms in case of a timing error.

On today's high-performance microprocessors, individual instructions may experience a considerable jitter in execution time. The concrete execution time of a given instruction depends on the processor state. This dependence can be hard to model, because multiple microarchitectural features, like pipelines, caches, branch prediction, and parallel execution, may be involved.

To illustrate the complexity of today's modern processors, consider the following description of the FreeScale MPC8641D microprocessor, taken from [CFG<sup>+</sup>10]: