# Developing a Simulator for the Hatfield Superscalar Processor

Department of Computer Science Technical Report No. 172

University of Hertfordshire

R. Collins

December 1993

#### **Abstract**

Researchers at the University of Hertfordshire's department of Computer Science are currently investigating the possibility of scheduling code at compile time for a new family of superscalar processors. This project has two main elements, the first being the specification of the architectural model for the superscalar processors and the development of a parametrised Superscalar Simulator program. The second element is an Instruction Scheduler program that will apply a global scheduling algorithm to the superscalar source assembly code. The overall objective of the project is increase and exploit the amount of instruction-level parallelism available by applying scheduling techniques at compile time, rather than by using the processor's hardware at run time. The Instruction Scheduler can take a global view of the whole source program and move code over large distances to expose the parallelism available. A conventional superscalar processor can only move code over small distances to enhance the available parallelism due to the limited 'window' of code that it examines at run time. By scheduling the code at compile time, the need for out-of-order instruction execution is eliminated and the processor's hardware can be greatly simplified leading to a 'minimal' superscalar.

This report deals specifically with the design and development of the Superscalar Simulator program and gives a detailed explanation of the main features of the architectural model adopted. The Hatfield Superscalar Processor (HSP) being developed can potentially execute many instructions in parallel and is designed to exploit the instruction-level parallelism that is present in general purpose computer programs. Features of the HSP's instruction set enable the parallelism detected by the Instruction Scheduler to be encoded into sequential source code so that the Superscalar Simulator can reconstruct the groups of instructions that can be safely executed in parallel. The sequential source code is compatible with all members of the HSP family and allows them to achieve high "speed-ups" over a normal RISC processor. A parametrised Superscalar Simulator is developed which enables a whole range of processor implementations to be studied and compared. The objective of the Superscalar Simulator is to run source code that has been passed through the Instruction Simulator and to identify the hardware features required that achieve near-optimal performance from a suite of general-purpose benchmark programs.

The report sets the HSP in the context of other recently studied approaches to exploiting instruction-level parallelism and discusses in detail the development of the Superscalar Simulator program. Initial results are given that show an encouraging degree of 'speed-up' over a conventional RISC type processor, but the full power of the Superscalar Simulator will not be realised until an Instruction Scheduler program has also been developed. The Simulator has many user-selectable features for studying a program's behaviour and can give a variety of statistical data to help analyse the results for a particular program run. Appendices are included that give the full instruction set specification for the Hatfield Superscalar Processor and a complete user's guide for operating the Superscalar Simulator program.

# Contents

|           |                                                     | Page No |

|-----------|-----------------------------------------------------|---------|

| Section 1 | Background                                          | 5       |

| 1.1       | VLIW Machines                                       | 5       |

| 1.2       | Superscalars                                        | 5       |

| 1.3       | Scheduling Code for a Minimal Superscalar           | 6       |

| Section 2 | Simulator Overview                                  | 8       |

| 2.1       | Elements of the Simulator                           | 8       |

| 2.2       | The Need for a Parametrised Model                   | 10      |

| 2.3       | User Facilities                                     | 10      |

| Section 3 | The Superscalar Instruction Buffer                  | 11      |

| 3.1       | Fetching Instructions from the Instruction Cache    | 11      |

| 3.2       | Modelling Instruction Buffer Behaviour              | 11      |

| Section 4 | Instruction Decode and Parallel Instruction Issue   | 12      |

| 4.1       | Selecting Candidate Instructions for Dispatch       | 12      |

| 4.2       | Data Dependencies                                   | 12      |

| 4.3       | Conditional Execution                               | 12      |

| 4.4       | Resource Constraints                                | 12      |

| 4.5       | Operand Availability                                | 13      |

| 4.6       | Removal of Instructions from the Instruction Buffer | 13      |

| Section 5 | Functional Units                                    | 14      |

| 5.1       | Types of Functional Units                           | 14      |

| 5.2       | A Common Pool of Resources                          | 14      |

| 5.3       | Pipelined and Non-Pipelined Implementations         | 15      |

| 5.4       | Data Forwarding and Result Bus Arbitration          | 15      |

| Section 6  | Register Files                                     | 16   |

|------------|----------------------------------------------------|------|

| 6.1        | A Pipelined View of Registers                      | 16   |

| 6.2        | Operand Availability                               | 16   |

| 6.3        | Invalid Data                                       | 17   |

| 6.4        | Speculative Execution                              | 17   |

| 6.5        | Write-After-Write Hazards                          | 18   |

| 6.6        | Special Purpose Registers                          | 18   |

| Section 7  | Modelling the Caches                               | 19   |

| 7.1        | The Instruction Cache                              | 19   |

| 7.2        | The Data Cache                                     | 19   |

| Section 8  | Branch Units                                       | 20   |

| 8.1        | The Branch Delay Count                             | 20   |

| 8.2        | Flushing Instructions from the Buffer              | 20   |

| 8.3        | Modelling the Fetch Unit Pipeline                  | 20   |

| 8.4        | Processing Branch Instructions                     | 21   |

| 8.5        | Handling Multiple Branches                         | . 22 |

| Section 9  | Processing in the Instruction Buffer               | 24   |

| 9.1        | "Squashing" Instructions in the Instruction Buffer | 24   |

| 9.2        | Scheduling Code for Delay Slots                    | 24   |

| 9.3        | Promoting Conditionally Executed Code              | 25   |

| 9.4        | Code Performance over a Range of Processors        | 26   |

| Section 10 | Assembler and Loader/Linker                        | 27   |

| 10.1       | Loading the Instruction Cache                      | 27   |

| 10.2       | Initialised and Uninitialised Data                 | 27   |

| 10.3       | Jump Lists                                         | 27   |

| 10.4       | Symbol Tables                                      | 27   |

| Section 11 | User Interface                                       | 29    |

|------------|------------------------------------------------------|-------|

| 11.1       | Defining the Machine Model                           | 29    |

|            | 11.1.1 Specifying Latencies                          | 29    |

|            | 11.1.2 Setting Buffer Parameters                     | 29    |

|            | 11.1.3 Altering Branch Behaviour                     | 30    |

|            | 11.1.4 Functional Capability                         | 30    |

| 11.2       | Tracing Facilities                                   | 31    |

| 11.3       | Statistical Data                                     | 32    |

| 11.4       | User Control Switches                                | 33    |

| Section 12 | Results to Date                                      | 34    |

| 12.1       | Simulator Performance on Different Host Computers    | 34    |

| 12.2       | The One-Pipe Model and Measuring "Speed-ups"         | 34    |

| 12.3       | The Stanford Benchmark Programs                      | 35    |

| Section 13 | Future Developments                                  | 39    |

| 13.1       | Extending the Model - Floating Point Capabilities    | 39    |

| 13.2       | Coping with I/O                                      | 39    |

| 13.3       | The Next Step - A Scheduler Program                  | 39    |

| Defe       |                                                      |       |

| References |                                                      | 41    |

| Appendix A | - The Hatfield Superscalar Processor Instruction Set | A1-7  |

| Appendix B | - A User's Manual for the Superscalar Simulator      | B1-28 |

# 1 Background

#### 1.1 VLIW Machines

One method of realising instruction-level parallelism is to schedule normal short RISC-like instructions into Very Long Instruction Words (VLIW) which are then executed, one per cycle, on a corresponding VLIW processor. Short instructions that can be executed in parallel with each other are placed in the same VLIW, with any unused space in the VLIW being padded out by NOP instructions. One advantage in this approach lies in the ability of an instruction scheduler to take a global view of the whole program at compile time so it can move code over great distances in order to realise extra parallelism. The scheduler must have detailed information about the target processor and its associated instruction latencies before it can correctly schedule the source code obtained from the compiler. By carrying out all the code motion at compile time, the processor hardware is greatly simplified and it can adopt an in-order policy for instruction issue. A HARP VLIW processor [4,5] has been developed at the University of Hertfordshire with the capability to execute four short instructions in parallel and much work has been done on developing suitable global scheduling algorithms that can exploit its potential for parallelism [7,15].

The main disadvantage of the VLIW approach is that code is scheduled for one particular processor implementation only and the source code must be recompiled if a different target processor is to be used. Users of computers understandably show a great reluctance to change their compiled program code when they want to update their hardware. Another problem is the increased size of the static code due to the need for NOPs to pad out unused portions of VLIWs. Finally, some algorithm, however simple, for predicting conditional branch behaviour must be assumed at compile time that may prove incorrect at run time. There is a consequential loss in performance as the machine discards instructions that were fetched from the wrong stream to take account of the mis-prediction. Some research [17] suggests that high accuracy in branch prediction could be a limiting factor to the overall parallelism achievable by both VLIW and superscalar machines.

# 1.2 Superscalars

An alternative strategy adopted by processor manufacturers [13,14] is to let the processor hardware find the parallelism at run time. Such processors are known as Superscalars and they operate on the normal sequential source code. The name "Superscalar" is chosen to distinguish these machines from other computers with parallel capabilities, such as Vector Processors, which are designed to manipulate the large data structure arrays commonly found in scientific code. The superscalar processor is capable of fetching several instructions from memory each cycle and these help to form a "window" of available instructions. This "window" is then examined for suitable candidate instructions that can be safely executed in parallel with each

other. This process involves testing for data dependencies between candidate instructions and the use of techniques such as "scoreboarding" or dynamically renaming registers so that instructions can be dispatched out-of-order.

The superscalar processor may also have mechanisms that keep a "history" of recent conditional branch behaviour that allow it to adjust dynamically to changes in program control flow. This flexibility can lead to higher accuracy in making branch predictions than is possible at compile time, although this point is still the subject of debate in recent research papers [18]. The main advantage seen by the user of computers based on superscalar processors is the code compatibility across a range of processor implementations, as they can all operate with the same sequential source code. Users are not required to recompile their programs when they update the hardware.

One serious disadvantage of the superscalar machine is the limited size of the "window" from which parallel instruction groups are selected, as there is no possibility of moving code globally. This limited view only allows for localised code compaction and will probably place an upper bound on the achievable parallel performance that falls far short of the potential parallelism available. There is also a problem with the increased circuit complexity required to detect data dependencies at run time and to handle the consequences of out-of-order instruction issue and dynamic register renaming.

# 1.3 Scheduling Code for a Minimal Superscalar

This project attempts to combine the best features from both of the previous approaches by scheduling code globally at compile time and encoding the parallelism found in sequential code so that it is compatible with a range of processors. Features of the HSP architecture should ensure that good performance is obtained on processor models with limited ability, even when code has been scheduled for a high-powered machine. In the machine model adopted, the number of instructions fetched each cycle is no longer directly linked to the number of instructions executed, but it is influenced by the size of the "Instruction Buffer" into which instructions are initially placed.

The need for dynamic renaming of registers and out-of-order issue is eliminated, thus greatly simplifying much of the circuitry found in a normal superscalar processor, leading to the concept of a "Minimal Superscalar". The HSP instruction set allows all instructions to be defined as conditionally executed on the basis of one or more Boolean registers. Removal of conditionally executed code whilst still in the Instruction Buffer can significantly reduce the number of functional units that are required to execute individual instructions in a given machine. At compile time, an Instruction Scheduler makes global movements on the source program code in order to form "parallel groups" of instructions that can safely be executed in the same time frame. Such groups are then used to fill the conceptual branch and load delay slots

that are assumed to exist on the target family of superscalar processors. Instruction scheduling also aims to promote code as high as possible in the sequential order, subject only to true data dependencies. The Instruction Scheduler will also be able to employ techniques such as software pipelining to optimise the performance of loops in order to increase the overall level of parallelism available.

A new type of branch instruction, with an explicitly defined "branch-dependent" region, is introduced that enables the parallelism exposed by the Instruction Scheduler to be preserved when the code is converted back into a sequential form suitable for the superscalar processors. Although code may be scheduled with a particular processor model in mind, it will still be correctly executed by any processor from the same family, regardless of its particular functional capabilities and latencies. It is hoped that the advanced features of the Hatfield Superscalar Processor will enable good performance to be obtained over a range of different processor models, all running on the same scheduled source code.

#### 2 Simulator Overview

#### 2.1 Elements of the Simulator

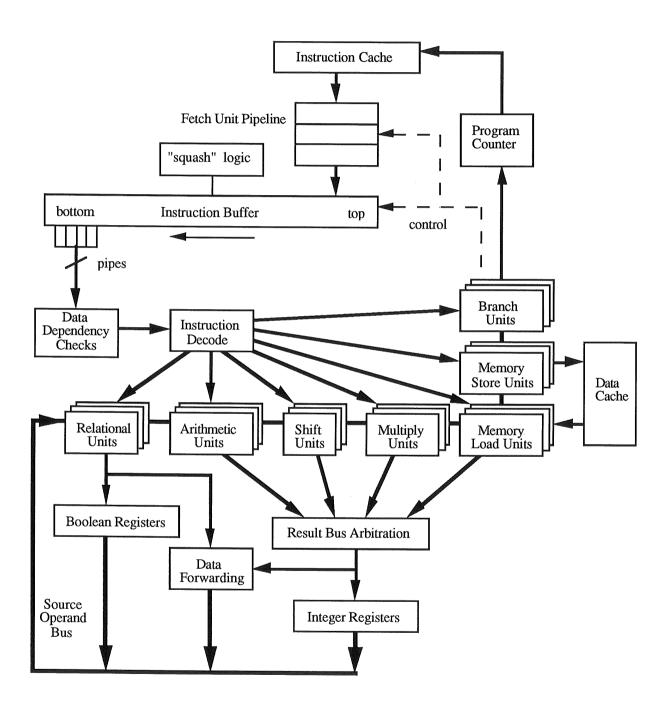

The Superscalar Simulator has four distinct stages in the processing of instructions from the Instruction Cache. The Instruction Fetch (IF) stage involves reading a block of instructions from the Instruction Cache and placing them into the top end of the Instruction Buffer. Instructions from the bottom end of the Instruction Buffer are selected for Instruction Decode (ID) and have their source operands accessed. The instructions being issued are passed to appropriate Functional Units which use the source operands when performing the Instruction Execute (EX) stage of processing. Finally, the Functional Units compete for a Result Bus and Write Back (WB) the results to the appropriate destination. Each of the four processing stages can take one or more clock cycles to complete, depending on the latencies for the different classes of instructions and cache memory access times. Individual instructions may also be forced to incur extra "wait" cycles while they are in the Instruction Buffer queue or in a Functional Unit that has unsuccessfully bid for a Result Bus.

All of the Simulator's important parameters can be altered by the user, starting with the Fetch Width that defines the size of block accessed from the Instruction Cache. The length of the Fetch Unit pipeline is determined by the number of Fetch Cycles for an Instruction Cache access. The Instruction Buffer itself has a maximum capacity defined by Buffer Size and functions as a FIFO queue. The HSP architecture has the ability to process several instructions in parallel as determined by the number of "pipes" provided in the model. Each cycle, new instructions are selected from the bottom of the Instruction Buffer to form an Instruction Decode (ID) group of data-independent instructions, each of which is assigned a "pipe". The "pipes" serve as routing devices that send the instructions to the appropriate Functional Units for execution. Potentially, each "pipe" can deliver an instruction to any unit in a common pool of Functional Units, but the allocation of resources is prioritised to select pipes containing instructions from earlier in the program sequence. Once the Functional Units have completed their processing they compete for a Result Bus in order to Write Back the results to the Register Files, and to Forward results to other Functional Units. The Memory Load and Memory Store Functional Units are the only units that interface directly with the Data Cache.

A Block Diagram of the complete Hatfield Superscalar Processor is shown in Figure 1 and the important elements illustrated will be discussed in detail in the following Sections.

Figure 1 Block Diagram of the Hatfield Superscalar Processor

# 2.2 The Need for a Parametrised Model

It is of great importance to provide a highly parametrised model of the Superscalar Simulator that allows a wide range of values to be adopted for all of the machine's features. This flexibility allows the potential benefits to be assessed for the most ambitious machine models without being over-constrained by considering implementational problems at this early stage. The machine model can then be "fine-tuned" to remove redundant or little-used hardware features and to investigate possible tradeoffs of performance against the functionality provided. Some of the most important parameters defining the Simulator model are shown in Table 1.

Fetch Capacity and Latency

Instruction Buffer Size

Parallel Issue Capability

Instruction Latencies

Type and Number of Functional Units

Number of Result Busses

Number of Integer and Boolean Registers

#### Table 1 Main Simulator Parameters

The Superscalar Simulator has been given substantial potential resources in the hope that these can be exploited by the Instruction Scheduler to achieve a high degree of instruction parallelism. Some recent research [11,12] suggests that theoretically the amount of instruction-level parallelism available in non-scientific code is an order of magnitude above that realised to date by proposed architectures. It is the aim of the project to attempt to increase realisable parallelism towards these theoretical upper bounds, hence the powerful Superscalar Simulator model.

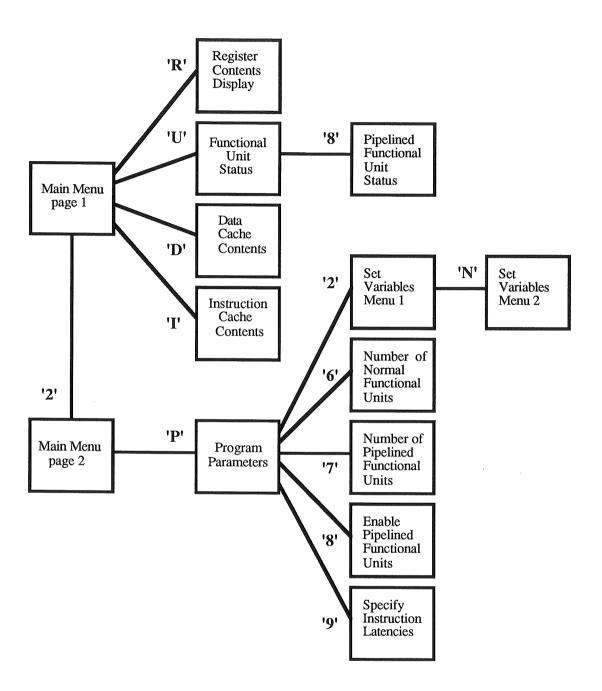

#### 2.3 User Facilities

A menu-driven interface is provided to alter any of the machine's individual parameters and to select a particular machine model. The user has the ability to examine the contents of the Instruction and Data Caches as well as the Integer and Boolean Register Files. Facilities are provided to record the "trace" of a program and to "single-step" through a program's execution, with full details of the internal workings of all the functional units being displayed.

Many user-defined parameters are also available that enable or disable aspects of the Simulator behaviour so that different features of the machine can be assessed quantitatively by comparing the results for different program runs. These control signals are also used to specify the amount and type of information displayed or recorded whilst a simulation is being carried out on a source program. Emphasis is placed on statistical data to help to evaluate the usage of the various machine resources provided by a particular Simulator configuration and to obtain a profile of the program's run-time behaviour.

# 3 The Superscalar Instruction Buffer

# 3.1 Fetching Instructions from the Instruction Cache

There is a need to simulate the use of a variable number of cycles for accessing instructions from the Instruction Cache. Technological advances mean that the machine cycle-time for new processors is likely to fall faster than equivalent improvements in cache memory access time. A Program Counter register is used to supply the Instruction Cache address. The size of each new group of instructions fetched is a control parameter, as are the number of cycles required. A Fetch Unit Pipeline data structure is used to simulate the variable number of cycles it takes to fetch instructions from the Instruction Cache into the Instruction Buffer. A group of instructions from the bottom of this Fetch Pipeline are copied into the top of the Instruction Buffer only if there is sufficient room for the whole group.

# 3.2 Modelling Instruction Buffer Behaviour

The Instruction Buffer functions as a FIFO queue where, each cycle, new groups of instructions from the Instruction Cache are read into the top of the Buffer, if there is room for them. Instructions from the bottom of the Instruction Buffer are selected for in-order dispatch to the Functional Units. Successfully dispatched instructions are marked as "squashed" in the Instruction Buffer and contiguous squashed instructions are removed from the bottom of the Buffer at the end of each cycle. Instructions in the Buffer can be also be marked as "squashed" to ensure that they are never dispatched and this use is described in more detail in Section 9. The Instruction Buffer can be fully or partially "flushed" upwards from a given point if a branch is found to be taken. The Fetch Pipeline can also be flushed of unwanted instructions when there is a change in program control flow. Some possible implementations of the Instruction Buffer hardware have been considered [2], with particular attention being paid to the interconnection problems that arise when routing instructions from the Buffer to the Functional Units.

#### 4 Instruction Decode and Parallel Instruction Issue

# 4.1 Selecting Candidate Instructions for Dispatch

The Simulator only dispatches instructions from the Instruction Buffer in strict program order. The first un-squashed instruction at the bottom of the Buffer receives priority and other unsquashed instructions can only be dispatched at the same time if there are no data dependencies between members of the group that is formed. Once a data dependency is detected, no further instructions from the Instruction Buffer can be dispatched in the current clock cycle.

### 4.2 Data Dependencies

The maximum number of instructions that can be dispatched concurrently is determined by a user specified parameter. Each new member of a group being formed for dispatch must check that none of the existing members can possibly alter one or more of the candidate instruction's source operands. If a data dependency is found no further instructions are added to the group, as out-of-order issue is not allowed. Members of this "Instruction Decode" group are then checked for source operand availability and then allowed to compete for Functional Units to execute the instructions. If a particular instruction from the Instruction Decode group is unable to obtain its source operands or find a suitable Functional Unit it will be "blocked" from proceeding, as will all instructions that follow it in the original sequential code.

#### 4.3 Conditional Execution

Any instruction can specify a number of Boolean conditions that must be met if the instruction is to be executed. Boolean values used for the conditional execution of instructions are obtained directly from the Boolean Register File, or they can be forwarded from a Functional Unit that is completing a relational or logical calculation. If it is found that the conditions for execution of an instruction in a Functional Unit are not met, the unit is re-initialised and the instruction discarded. Any Functional Unit that is re-initialised in this way will not compete for a Result Bus and will be available to take a new instruction in the next machine cycle.

#### 4.4 Resource Constraints

The number and type of Functional Units provided by the Simulator are specified by the user, with pipelined or non-pipelined versions being available for most types of instructions. The Functional Units form a common pool of resources that are available to any of the instructions in the Instruction Decode group on a first-come first-served basis. If an instruction is to be executed it competes with other instructions for an available Functional Unit of the correct type,

with priority being given to instructions that appear earlier in the program sequence. If an instruction is unable to secure a Functional Unit, it is "blocked" and no instructions that follow it can be dispatched.

# 4.5 Operand Availability

Once an instruction from the Instruction Decode group has successfully secured a Functional Unit, the instruction is passed to that unit along with the appropriate source operands. If source operand values are unavailable in the Main Register files this indicates that a new value is currently being computed by one of the Functional Units from an instruction that was issued earlier. A check is made to see if the new value is available from a Functional Unit that completed its work last cycle but has still to Write Back the result to the Main Registers. If any of the source operands are still unobtainable, the candidate instruction is "blocked" and no further instructions from its Instruction Decode group are dealt with this cycle. All instructions that are successfully dispatched to Functional Units are marked as "squashed" in the Instruction Buffer.

#### 4.6 Removal of Instructions from the Instruction Buffer

At the end of each cycle the Instruction Buffer is examined from the bottom upwards and all instructions marked as "squashed" are removed, up to the first non-squashed instruction. The remaining instructions in the Buffer, squashed or un-squashed, are then counted and deducted from the maximum Buffer capacity in order to determine if there is sufficient room for the next group to be fetched in from the Instruction Cache. Instructions that are marked as "squashed" which are within the main body of "valid" instructions will not be considered for the next Instruction Decode group. Squashed instructions that are preceded by un-squashed instructions cannot be removed completely from the Buffer at this stage as they convey positional information that is needed to process Branch instructions correctly. The method used to convey the scope of the branch-dependent region relies on a Branch count that is associated with each Branch instruction. The Branch Count gives the position of the last branch-dependent instruction relative to the position of the Branch instruction itself, so it is essential to preserve the correct spatial representation when the instructions are in the Instruction Buffer. Any valid instructions that were unsuccessfully selected for dispatch this cycle will remain in the Buffer and will form part of the next Instruction Decode group.

### 5 Functional Units

# 5.1 Types of Functional Units

The HSP instruction set supported by the Superscalar Simulator, (Appendix A), includes most of the iHARP [1] instructions and has been split into different types, partly according to the nature of the destination specified by the instruction and latency considerations. By using this method of categorisation it is hoped to be able to simplify the hardware implementation of the processor by physically grouping Functional Units of a particular type around register files which they target as destinations. This approach should simplify the interconnection complexity that will exist in a processor with high parallel capabilities. There are seven types of Functional Units, as shown in Table 2.

Arithmetic

Relational (Boolean)

Multiply

Shift

Memory Load

Memory Store

Branch Units

Table 2 Functional Unit Types

At present, Memory Load and Memory Store capabilities are independent of each other but the machine model may be altered in the future to combine these into a single Memory Access capability. One possible Data Cache implementation could involve the use of two dual-ported caches, each holding the same data at all times. A Memory Store would then be required to write to both caches simultaneously, to ensure data coherency, and would use one port on each. Such an implementation could allow parallel access for 4 Memory Loads, or 2 Memory Stores, or 1 Memory Store and 2 Memory Loads. Until a clearer picture emerges of the likely demands on the Data Cache made by code that has been fully scheduled, implementation issues will be put to one side and the current orthogonal approach will be maintained.

#### 5.2 A Common Pool of Resources

The maximum number of instructions that can be dispatched for execution in a cycle is specified by the user as the number of "pipes". Unlike the HARP approach [4], these pipes have no particular individual processing capabilities in their own right but can be thought of as "conduits" that route instructions, along with their source operands, to the appropriate type of

Functional Unit. By supplying a common pool of Functional Units that are available to any one of the individual pipes it is possible to economise on the number of Functional Units provided. The exact number and mixture of different types of Functional Unit that comprise the resource pool can be altered to closely match the likely needs of scheduled general purpose code, with a trade-off between the savings in chip complexity against the increased risk of a "blocked" instruction occurring. It is desirable that the number of Functional Units provided should be kept as low as possible to reduce the interconnection problem for the hardware and it is also important that each unit should spend as much time as possible executing useful code.

# 5.3 Pipelined and Non-Pipelined Implementations

All units are available in pipelined or non-pipelined forms, with individual latencies being specified by the user. Non-pipelined Functional Units can only work on one instruction at a time and are unavailable for new input for a number of cycles depending on the latency associated with each type of instruction. Pipelined units are always available for new input each cycle unless they are "stalled" due to a resource restraint at their output when they compete for Result Busses. One exception to this scheme is when Arithmetic Units are used to execute integer Divide instructions. As Divide instructions occur infrequently in general-purpose code they do not justify their own separate category of Functional Unit. Instead, the Arithmetic Units are forced to adopt the latency associated with the Divide instruction rather than the normal arithmetic latency. In the case of Pipelined Arithmetic units, the processing of a Divide means that the input can be blocked for several cycles, depending on the relative difference in instruction latencies. Branch Units are different to other Functional Units in that they can complete their work during the Instruction Decode (ID) phase and have a fixed latency of one.

# 5.4 Data Forwarding and Result Bus Arbitration

The last task of a Functional Unit is to Write Back the result to the appropriate Main Register file. If an instruction requires to access this new value as one of its source operands it is advantageous to provide some means of "forwarding" the new value between Functional Units, without having to wait for the Write Back to complete. However, the number of Result Busses for integer values is specified by the user and Functional Units must compete for their use. Only those units that secure a Result Bus can complete during the current cycle and forward their results on to other units. Functional Units that are unsuccessful in obtaining a Result Bus are forced to "stall" but will receive preferential treatment in the next arbitration round. Pipelined Functional Units that have their output stalled in this way will still be available to take a new instruction next cycle, unless all of their pipeline stages are already fully occupied. Sufficient Boolean Result Busses are provided to cope with the maximum possible demand, so there is no need to perform any kind of bus arbitration.

# 6 Register Files

# 6.1 A Pipelined View of Registers

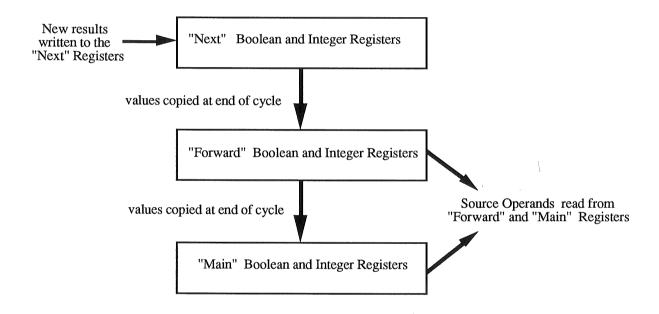

In order that the Simulator can achieve the functionality required by the HSP model, it is convenient to model three banks of Integer and Boolean Registers which can be viewed as a "register pipeline". The three stages are represented by the "Next", "Forward" and "Main" register files. Functional Units that are completing their function during the current cycle will write their results to the "Next" register bank. At the end of the cycle all functional units that are still actively computing a result will mark the appropriate Main Registers as unavailable. The Main Register file is updated from the Forward Registers, which in turn take in the new values from the "Next" register file. This process is illustrated in Figure 2 where Functional Units write new results into the Next file but obtain source operands from the Forward or Main files.

Figure 2 Register Files

# 6.2 Operand Availability

The source operands specified by an instruction are identified in the ID stage and made ready for the designated Functional Unit to access during the EX stage. It is essential for the processor model that access to the registers is performed prior to an instruction's execution if the machine cycle time is not to be unduly extended. However, in the Superscalar Simulator it is implementationally convenient to allow the Functional Units to perform these register accesses during the EX stage. Functional units requiring source operands will first look in the "Main"

registers and if these are marked as unavailable the "Forward" registers are examined to see if the required value was calculated last cycle. As new results from the Functional Units are always written first into the "Next" file, there is no possibility of undesirable side-effects in the Simulator when requesting source operands. Source operand values are taken from the Main or Forward registers and cannot be influenced by a new result being computed during the same cycle as these always target the Next register files.

#### 6.3 Invalid Data

All the Register Files have a flag which can indicate that the data they contain is "invalid". This feature serves two purposes. Firstly it enables Speculative Execution of instructions to be supported and secondly it acts as a useful debugging tool when running diagnostic programs. The user may choose to mark all the Main registers as "invalid" at the start of a program run, and these will only become "valid" when a functional unit writes in a new value. If the program tries to access a source operand that is "invalid" an error message is given to indicate a possible programming error. Many real benchmark programs have procedures that start by automatically storing away in memory the contents of any registers that they will be using, regardless of their present contents. It is necessary to mark all registers, or possibly a subset identified by the compiler, as "valid" before starting to run a program of this nature or false error messages will occur.

### 6.4 Speculative Execution

It is possible that an instruction scheduler could move an instruction speculatively above the conditional branch that controls entry to the instruction's original location. Such an instruction may now be executed unconditionally, before it is known which way the conditional branch will go. If the promoted instruction causes an exception, such as arithmetic overflow, the program will be forced to terminate, even if this instruction was originally on the branch path that is not taken. A speculatively promoted Memory Load instruction could produce an invalid memory address that would also cause an exception when the Data Cache is accessed. A special marker is used in the HSP architecture to indicate that the promoted instruction is a Speculative Instruction and this inhibits any exception errors from occurring. The destination register of such an instruction is instead marked as "invalid" so that if a non-speculative instruction tries to access the register as a source operand, a trap is forced. Any instruction can be marked as Speculative except for Memory Store instructions as these permanently alter the machine state. One possible strategy that could support the speculative execution of Memory Store instructions is to introduce a Write Buffer for the new values rather than allowing the memory to be altered straight away. The HSP architecture does not encompass such a scheme at present.

#### 6.5 Write-After-Write Hazards

Instructions may be held up due to anti-dependencies, or write-after-write (WAW) hazards. Anti-dependencies, also known as Write-After-Read (WAR) hazards, occur when the destination register of an instruction is the source register of an earlier instruction and these can be dealt with in the Instruction Scheduler by register re-naming. In WAW hazards an instruction issued earlier is still computing a result for a register that is also the destination for the instruction currently being issued. If the latter instruction is issued and completes before the earlier instruction has completed, there is a danger that the final value stored into the destination register will be incorrect. The Simulator offers two strategies to cope with the problem as it has not yet been decided which scheme should be encompassed in the HSP architecture. The first approach is to insist that instructions are held up until all previously issued instructions with the same destination have been completed. The second approach is to inhibit the Functional Unit that is handling the earlier instruction and to issue the second instruction as normal. Any Functional Unit that is inhibited will not compete for the Result Busses and will become available for new instructions in the next cycle. It is safe to inhibit instructions in this manner as there are no instructions waiting for the redundant result from the earlier instruction due to the fact that instructions are never issued out-of-order. Any Read instruction that is data dependent on the first Write will be forced to hold up until the new result is in the Forward Registers so a second Write issued in parallel with the Read cannot have adverse side-effects. A choice of Simulator behaviour for dealing with WAW hazards can be specified by the user.

### 6.6 Special Purpose Registers

Some special purpose registers are provided for the convenience of the compiler when it is dealing with "ORed" addressing [16] and procedure calls. Two pointers into memory are provided, Global Pointer (GP) and Stack Pointer (SP), that are used as base addresses for global data objects and stack frames respectively. There is a Status Register (SR) which can be used to hold the contents of the Boolean Register file so that this information can be easily stored away in memory on a procedure call. Lastly a second Stack Pointer (SP') is also provided as this can be used to reference an earlier stack frame. The SP' register is included to support code that was originally compiled for the HARP model from Modular 2 source code where scope rules for program variables need to be enforced. All four registers are arbitrarily mapped into Integer Registers reserved for this purpose, as specified in a global header file.

# 7 Modelling the Caches

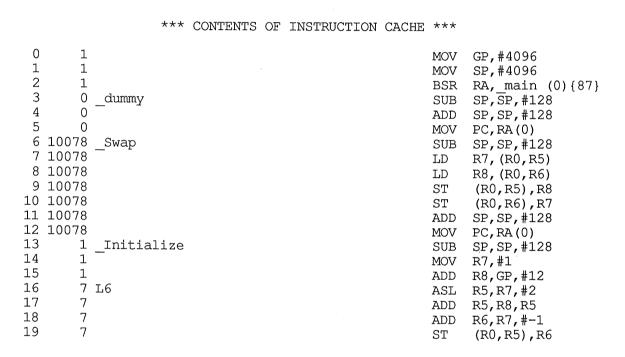

#### 7.1 The Instruction Cache

As the Superscalar Simulator is only concerned with modelling the functionality of the Superscalar Processor, there is no restriction on the data structures that can be used to represent the Instruction Cache. This freedom of choice means that a structure can be chosen that helps the Simulator run faster by holding instructions in a decoded form, even though this requires larger amounts of memory storage on the host computer. As a new program file is read into the Simulator, the individual instructions are decoded and the relevant fields of an Instruction Record are filled. The Instruction Cache consists of a contiguous linear array of pointers to instruction records to represent the source program code. Facilities in the Simulator allow the user to examine any part of the Instruction Cache and to display an instruction in the original assembler code or as an abstract instruction record. Individual locations in the Instruction Cache can be edited by the user, possibly to alter program constants between program simulation runs.

#### 7.2 The Data Cache

The Data Cache consists of an array of pointers to data elements, each of which can hold a 32-bit value and an optional label to aid readability for the user. Procedures that access the Data Cache convert any memory addresses into an array index by dividing the address by the number of bytes in a word, which is currently defined by a global constant as four. In order to conserve memory on the host computer, the Data Cache is declared as an array of pointers according to a global constant that specifies the size of the array. Individual Data Elements are allocated storage space as and when they are accessed by the program being executed. This policy means that at the end of a program run the Data Cache will have only created elements for those locations used by the program. When the Data Cache is displayed to the user only elements that were used by the program are visible, which aids readability.

If a program source file specifies initialised data, the appropriate data elements are created and loaded with data. The Data Cache is byte-addressable and this is implemented by reading and writing complete words but only altering the specified byte within the word. Half-word accesses to memory are not supported by the HSP architecture. Functional Units that perform Memory Loads and Memory Stores have their own particular instruction latencies, which can be different from each other and from the latency associated with accesses to the Instruction Cache.

The Simulator keeps track of new data values on their way to Data Cache locations by modelling a Memory Store Pipeline. Any Memory Load instructions first check if the latest value for the required memory address is in the Memory Store Pipeline before looking in the Data Cache itself. This process ensures that the correct value is obtained and means that the machine does not have to wait for the Memory Store to complete before the new value can be accessed.

#### 8 Branch Units

## 8.1 The Branch Delay Count

A branch instruction appearing in sequential code must convey to the Superscalar processor some sense of the amount of code that has been scheduled into its "branch delay" slot. A Branch Count can be associated with every branch instruction to indicate the scope of this "branch-dependent region". When the Simulator executes a branch instruction it first determines if the branch is to be taken. A taken branch with a Branch Count of zero causes all instructions following that branch to be flushed from the Instruction Buffer and from the Fetch Pipeline, as well as inhibiting the processing of later instructions from the same Instruction Dispatch group as the branch itself. The contents of the Program Counter are then altered to the new value specified as the branch target address. New instructions will be fetched from the branch target address during the next cycle.

If the value of Branch Count is greater than zero, checks must be made to ensure that the correct number of following instructions are allowed to be processed before dealing with any new instructions from the branch target stream. The Branch Count therefore specifies a "protected region" of instructions that follow the branch which must always be considered for execution, irrespective of how the branch instruction evaluates, and is therefore analogous to a branch delay slot in a conventional pipelined machine.

# 8.2 Flushing Instructions from the Buffer

When a branch is taken there may be a need to flush out instructions from the Instruction Buffer that have been pre-fetched from the sequential successor stream and that are no longer required. The Simulator removes these unwanted instructions from a point in the Instruction Buffer that depends on the position of the taken branch instruction and the value of its Branch Count. The newly freed Buffer locations increase the overall space that is available in the Instruction Buffer for it to accept a new group of instructions from the Fetch Unit towards the end of the same cycle.

### 8.3 Modelling the Fetch Unit Pipeline

Latencies associated with the fetching of instructions from the Instruction Cache are implemented by a pipeline of Fetch Registers. The user specifies how many instructions are to be fetched each cycle and this determines the width of the Fetch Unit. The length of the Fetch Pipeline is determined by the Fetch Latency. The top row of the Fetch Unit is filled with a new group of instructions from the Instruction Cache, from an address specified by the Program Counter. The Program Counter value is then adjusted to reflect the number of instructions

successfully read from memory during the current cycle. Instruction groups are then copied into each row of the Fetch Unit from the row above and instructions from the bottom of the Fetch Unit enter the Instruction Buffer, provided there is enough space for them.

If there is insufficient space in the Instruction Buffer to take a complete group of instructions from the Fetch Unit, no new instructions are put in the Instruction Buffer and the group remains in the bottom row of the Fetch Unit. If other stages of the Fetch pipeline are also occupied, a failure to load the Instruction Buffer will result in the Fetch Unit "stalling" and no new instructions will be fetched from the Instruction Cache during this cycle. Instruction positions in the Fetch Pipeline can be marked as "valid" and "squashed". When an instruction first enters the Fetch Unit from the Instruction Cache it is marked as "valid" to indicate that the position is occupied by a real instruction. When a branch is found to be taken, one or more whole rows in the Fetch Unit may be "flushed" by marking the relevant positions as "invalid". If some of the contents of a Fetch Unit row are to be preserved after a branch, due to a non-zero branch count, the whole row cannot be re-initialised so the redundant instructions are marked as "squashed" instead. Instructions that appear in the bottom of the Fetch Unit which are marked as "squashed" will not be considered when transferring a group of instructions to the Instruction Buffer. In order that the Simulator can model a Fetch latency of just one cycle, the length of the Fetch Pipeline is always one more than the Fetch latency. This means that normally the bottom row of the Fetch Unit Pipeline contains instructions that have also just been entered into the Instruction Buffer.

# 8.4 Processing Branch Instructions

Branch instructions differ from other types of instruction in that they perform the bulk of their work in the Instruction Decode stage rather than the Execution Stage. When a Branch instruction is considered for dispatch, an available Branch Unit is found and processing carried out during the same ID cycle. If the Branch evaluates as not taken, no further action is required so the Branch Unit is cleared and returned to the common pool of Functional Units to become available again in the next cycle.

If a branch is found to be taken there are several different cases that can arise which will require the HSP architecture to behave in different ways. When the Branch Count is zero, no instructions following the branch are to be executed and the Instruction Buffer can be flushed from the branch location upwards. Similarly, the Fetch Unit is completely flushed and all subsequent instructions from the Instruction Decode group are inhibited. The PC is then altered to the branch target address and the branch unit has finished its task.

When the Branch Count contains a non-zero value, the last branch-dependent instruction may be in the Instruction Buffer, or it may be on its way through the Fetch Unit pipeline, or it may not have been fetched from the Instruction Cache. A search is first made in the Instruction Buffer to

see if it contains the last branch-dependent instruction. In this case the dependency is said to have been "satisfied" and it is safe to flush the Instruction Buffer from beyond the last dependent instruction and to completely clear out the Fetch Unit. Again, instructions that follow the branch in the same Instruction Decode group must be inhibited if they come from beyond the last branch-dependent location in the Instruction Buffer. The new value for the Program Counter then takes effect and the Branch Unit finishes processing at the end of the cycle.

The second case to consider is when the last branch-dependent instruction cannot be found in the Instruction Buffer itself but is already somewhere in the Fetch Unit pipeline, on its way from the Instruction Cache. Instructions in the Fetch Unit are preserved up to the last branch-dependent instruction, with following locations being marked as "squashed" or "invalid". No instructions in the Instruction Buffer are flushed and all other members of the Instruction Decode group are allowed to continue as normal. The new value for the Program Counter then takes effect and the Branch Unit finishes processing at the end of the cycle.

The last case to consider when processing a branch instruction that is found to be taken is when the last branch-dependent instruction has not yet been fetched from the Instruction Cache. A count is made of the number of occupied positions in the Instruction Buffer that follow the branch instruction and this is added to the number of valid un-squashed instructions in the Fetch Unit pipeline. This combined total is deducted from the Branch Count specified in the branch instruction to yield a figure that represents the "short-fall" of dependent instructions still required to be fetched. The value of the "short-fall" is stored in the Branch Unit which will then continue to process the branch instruction in subsequent cycles. There may be several cycles before the last branch-dependent instruction is detected in the Fetch Unit and during each cycle the short-fall value is recalculated to take account of the actual number of valid instructions in the Instruction Buffer and the Fetch Unit Pipeline. Only then can the new value for the Program Counter take effect and the Branch Unit finish its processing.

### 8.5 Handling Multiple Branches

It is possible that branch instructions may be moved by an Instruction Scheduler so that they appear within the branch-dependent range of an earlier branch instruction. When an Instruction Decode group is being processed for dispatch to the Functional Units, there may be several branch instructions in the same group. As long as there are sufficient Branch Units, all the branch instructions can be dispatched, subject to the normal data dependency checks. Any number of branches that evaluate as not-taken can be processed in parallel, up to and beyond the first branch that is found to be taken.

Once a taken branch is found, its Branch Count may inhibit other instructions from the same Instruction Dispatch group from being executed. If a second surviving branch instruction from the same Instruction Decode group also evaluates as being taken, it is not allowed to take effect

during the current cycle even if its Branch Count can be satisfied. Only one branch instruction that evaluates as being taken can be allowed to alter the Program Counter in any one cycle. The second branch taken will be dealt with in subsequent cycles when its Branch Count will be reappraised to determine if its branch-dependent region has been satisfied. This decision will depend on the modified state of the Instruction Buffer and Fetch Unit occupancy caused by the processing of the first branch's Branch Count. Processing of the first branch could cause instructions to be flushed from the Instruction Buffer that were within the scope of the second branch's dependent region.

It is also worth noting that this strategy implies that a branch instruction within the branch-dependent region of an earlier branch instruction, must itself have a branch-dependent region that extends at least as far as that of the first branch instruction. This relationship between "nested" branches will always be the case if the code has been scheduled correctly.

# 9 Processing in the Instruction Buffer

# 9.1 "Squashing" Instructions in the Instruction Buffer

In the normal course of events valid instructions enter the top of the Instruction Buffer from the Fetch Unit and move down to the bottom end of the Buffer from where they are selected as members of the next Instruction Decode group. Once an instruction has been successfully dispatched to a Functional Unit it is marked as "squashed" in the Instruction Buffer. Towards the end of the cycle, all contiguous squashed locations from the bottom end of the Instruction Buffer are removed, freeing up more space for incoming instructions from the Fetch Unit. When a branch is found to be taken, some or all of the locations in the Instruction Buffer may be marked "empty" as the unwanted instructions are flushed out.

Instructions in the Instruction Buffer may be also be marked as "squashed" in order to prevent them from ever being dispatched to Functional Units. While the latest Instruction Decode group is being formed and processed, all conditionally executed un-squashed instructions that are resident in the Instruction Buffer are examined to see if any of them can be safely eliminated. The bit-masks that encode the conditions to be met for the execution of each instruction are compared with the latest Boolean values, with new result values being forwarded from Relational Units that completed their calculation during the previous cycle. If one or more of the conditions necessary for execution is definitely not met the instruction in the Buffer can be safely "squashed" at the end of the cycle. As only un-squashed instructions are considered for inclusion in the Instruction Decode groups, this means of squashing instructions in the Instruction Buffer effectively alters the code that is dispatched to the Functional Units in the following cycle. One restriction to the squashing of conditionally executed code in the Instruction Buffer is that a test must be made to ensure that there is no un-squashed relational instruction ahead of the candidate to be squashed which could potentially alter the value of the Boolean upon which the decision to squash uniquely depends. The ability to squash instructions before they are considered for dispatch is put to good use in Section 9.3.

# 9.2 Scheduling Code for Delay Slots

One of the biggest problems in enhancing the performance of pipelined machines is to eliminate the branch penalty that is suffered whenever a branch is taken. This penalty is due to the need to flush out unwanted instructions from the sequential successor stream, leaving the processor nothing to do for one or more cycles while it waits for new instructions to arrive from the branch target stream. By using a delayed branch mechanism the processor is instructed to always execute instructions scheduled in the branch delay slots, irrespective of whether the branch is taken or not. This approach ensures that the processor is kept busy with useful instructions while new instructions are being fetched from the branch target address, but it relies on the Instruction Scheduler being able to fill the delay slots successfully with useful code.

Suitable candidate instructions can usually be found to fill the first branch delay slot but subsequent slots become progressively harder to fill [21]. The problem is magnified in a parallel machine where the number of instructions required to keep the machine busy is greatly increased. Traditional machines may be forced to suffer the branch penalty in terms of lost machine cycles each time the branch is take. The HARP project adopted a strategy of promoting conditionally executed code into the delay slots according to some branch-prediction algorithm. In such a scheme a penalty is suffered every time a branch is mis-predicted. A result of this observation is that much work is being carried out by other researchers on developing algorithms and hardware mechanism that attempt to achieve high branch prediction accuracy in high-performance superscalar machines [6,9,10,17].

# 9.3 Promoting Conditionally Executed Code

It is thought that the ability of the HSP architecture to dynamically alter the instruction sequence seen by the processing elements of the machine will be of crucial importance to the Superscalar's overall performance. If code is promoted into the conceptual branch delay slots from the branch target stream, rather than the sequential successor stream, it can be made to be conditionally executed on the same Boolean value that is controlling the branch instruction itself. Assuming that the branch control Boolean is calculated by a relational instruction immediately preceding the branch instruction, the new result will come through too late to effect the make-up of the Instruction Decode group containing the branch.

If the branch is not taken, the new Boolean value can be used to squash all of the Instruction Buffer code that was promoted into the branch-dependent region. In the following cycle the new Instruction Decode group can be selected from the sequential successor code that follows the branch-dependent region, if this has been pre-fetched into the Instruction Buffer. In general the fetch-rate exceeds the average dispatch-rate and the sequential successor code will have been pre-fetched into the Instruction Buffer by the time the branch instruction is being executed.

If the branch is taken, the promoted code from the branch target stream survives and provides the processor with useful instructions to be executed while the rest of the Instruction Buffer is flushed out and new instructions are being fetched from the branch target address. This mechanism should ensure that there is no branch penalty when the branch is taken, without slowing up the processing of the sequential successor code when the branch is not taken. It could also eliminate the need for complex branch prediction strategies for filling branch delay slots by adopting a simple scheme where code from the branch target is always selected for promotion. One exception to this rule may be procedure calls to library routines which are not in the scope of the Instruction Scheduler at compile time, thus making code promotion from the branch target impossible. Also, branch instructions that alter control flow at the end of a procedure call may have unfilled branch delay slots as the return address is determined dynamically at run time.

There still remains a need to use some scheduling algorithm for promoting code that is to be conditionally executed in parallel with the branch instruction itself when the new value of the controlling Boolean may not yet be known.

# 9.4 Code Performance over a Range of Processors

An important advantage that superscalar processors have over equivalent VLIW machines is their ability to be code-compatible with each other. The source program code need only be compiled once to be acceptable to a whole range of different superscalar processors, each processor having different capabilities and instruction latencies. A consequence of this code compatibility is that a customer using one type of superscalar processor can up-grade the hardware to a more powerful machine without the necessity to recompile all the programs that are being run on the current computer.

However, code that has been scheduled with a particular superscalar implementation in mind may not run very efficiently on a processor with different capabilities. This drop in performance could be particularly noticeable when code scheduled for a machine with, say eight pipelines, is run on a processor with only four pipes. There is a danger that by promoting sufficient code into the branch-dependent region such that eight pipes can be kept busy, the four-pipe model is forced to waste several cycles ploughing through conditional code that is destined to be discarded whenever the branch is not taken.

The ability to squash conditionally executed code that is resident in the Instruction Buffer enables a Superscalar processor with a limited number of pipes and Functional Units to still achieve a high performance when dealing with code scheduled for a more powerful machine. The overall effect is to achieve a graceful degradation in performance as the processor implementation model is reduced from that assumed when scheduling the code. It may even be found that by assuming unlimited hardware resources when first scheduling the code, good performance is still achieved on all but the most restrictive of processor models.

#### 10 Assembler and Loader/Linker

# 10.1 Loading the Instruction Cache

The Simulator provides facilities that enable assembler source files to be selected by the user and read into the Instruction Cache so that they can be run on the machine model specified by the user. The original C code has first been passed through a "gnucc" compiler that produced the correct format of assembler mnemonic code, together with assembler directives and data allocation commands. The assembler code is relocatable, with branch targets and data references being expressed as labels rather than actual addresses in memory. All instructions are decoded to create Instruction Records which are placed in the Instruction Cache.

#### 10.2 Initialised and Uninitialised Data

Certain assembler directives specify a data label and a requirement to reserve a number of bytes in the Data Cache as uninitialised data space. As each such directive is encountered an appropriate amount of memory is allocated, starting at a specified base address, and an entry made in a Data Cache Symbol Table for the data label and its memory address. Initialised data is dealt with in a similar fashion except that actual data is read into the memory locations that have been allocated in the Data Cache.

### 10.3 Jump Lists

The compiler may produce structures known as Jump Lists when it compiles "switch" statements in the C source program. These Jump Lists take the form of a "label" followed by a list of labels. Each Jump List must eventually be mapped into a region of data memory. The first label is entered in a symbol table and allocated a Data Cache address. The list of labels refer to instructions in the Instruction Cache and must be translated into the appropriate Instruction Cache addresses before being stored as data values in the Data Cache. These Jump Lists are encountered whilst reading in the assembler source file and contain labels that make forward references to code that has not yet been read in. It is not possible to fully translate all the Jump List labels whilst still reading in the source program so temporary data structures are used to hold the information until all the symbol tables have been created.

#### 10.4 Symbol Tables

Symbol tables provide a means of recording the actual addresses allocated to all labelled instructions and data structures. These tables are then used to "bind" the code that has been read into the Instruction and Data Caches by replacing references to labels with real address values.

After the Instruction Cache has been loaded, it is scanned through by the Simulator and an Instruction Symbol Table is created. The Instruction Symbol Table can then be used to process the abstract Jump List structures, which in turn enter the correct address values in the corresponding jump tables formed in the Data Cache. The temporary Jump List structures are then no longer required and are deallocated.

The Instruction Symbol Table is combined with the Data Symbol Table to form a Working Symbol Table. The Simulator also contains a Library Symbol Table that is designed to deal with standard procedure calls made by a source program for which the code has not been supplied. Typically these will be calls requiring Input/Output such as "printf" or "scanf" and will be handled in the Simulator by making system calls to the host computer on which the Simulator is being run. The Library Symbol Table contains reserved Data Cache addresses, a sort of autovector address, which can be picked up by the Simulator at run time in order to implement the relevant procedures. Any instruction that attempts to perform a memory access to such a reserved Data Cache address will cause the Simulator to make the appropriate system call. The compiler must have details of the actual method used by the Simulator for passing parameters to such procedures in order that the code to access the correct register values is produced.

Lastly, the Library Symbol Table is appended to the Working Symbol Table which is then used to bind all the data and instruction labels referred to by instructions contained in the Instruction Cache.

#### 11 User Interface

# 11.1 Defining the Machine Model

# 11.1.1 Specifying Latencies

The Simulator offers the user the opportunity to define the parameters that govern many details of the machine model's behaviour. Before starting a program run, the user can display the current parameter settings that are in force and then edit these via the menu options as required. The individual latencies associated with the different types of Functional Units can all be altered, normally in the range one to four, except for Branch Units which always have an associated latency of one. Also Multiply and Divide instructions have extended latency ranges of one to six and one to 32 respectively. Similarly, the number of cycles it takes to access instructions from the Instruction Cache is determined by the Fetch latency, which can be set to a value between one and four. If the Fetch latency is set to one it represents a machine with one branch delay slot while a setting of four would imply a branch delay of four cycles.

A Memory Load latency of one can be selected to model a machine where the "ORed" mechanism is used for Data Cache address calculation. In such a model the value accessed from memory in one cycle is made available via forwarding in the next cycle and there is no Load delay slot. The impact of performing a conventional address calculation by adding two component parts can be modelled by increasing the latency for Memory Load by one cycle and this introduces a Load delay of one cycle.

It will be the job of the Instruction Scheduler to find ways of filling these branch and load delay slots with useful code in order to prevent the branch penalty from seriously limiting machine performance. The Instruction Scheduler will assume a machine model with the longest possible branch and load delays, as well as the maximum envisaged amount of machine resources. The flexibility provided in defining latencies also enables machines to be modelled where processor cycle time is much less than cache access time and allows for non-integer ratios between these two quantities, such as a fetch latency of three cycles with an arithmetic latency of two cycles.

### 11.1.2 Setting Buffer Parameters

The Instruction Buffer plays an important part in the Superscalar machine and may prove essential in achieving good performance from highly scheduled code, particularly for machines with several branch delay slots. The user can alter several parameters that will define the model to be used for the Instruction Buffer. The maximum size of the Buffer can be set to any value in the range one to 256. The number of new instructions fetched each cycle from the Instruction Cache is determined by Fetch Width, which can be in the range one to 32. The Fetch Width selected must not be larger than the Maximum Buffer Size otherwise no instructions will ever be

successfully fetched into the Instruction Buffer.

A flag signal can be set by the user to disable conditionally executed instructions from being squashed in the Instruction Buffer, so that comparisons can be made between program runs that, hopefully, will show the power of this important machine feature. Another signal can be set to hold up the issuing of instructions, if a Write-After-Write dependency is detected, until the earlier instruction with the same destination has finished being processed.

### 11.1.3 Altering Branch Behaviour

The Simulator model provides for three alternative implementations of Branch instructions and their action is closely coupled with the models used for the Instruction Buffer and the Fetch Pipeline. The most powerful model adopted is that described in earlier sections where a branch instruction is always issued to a Branch Unit, if one is available. The branch instruction remains in the Branch Unit until its last branch-dependent instruction is detected in the Instruction Buffer or the Fetch Pipeline, at which time the Program Counter is altered and unwanted instructions are removed.

A second model for Branch behaviour is possible where a taken Branch instruction will be blocked in the Instruction Buffer until the last branch-dependent instruction is in the Instruction Buffer or on its way via the Fetch Pipeline. If a Branch instruction is held up in the Instruction Buffer, no instructions following the Branch will be issued as the HSP architecture only dispatches instructions on an in-order basis. This restriction means that the processor could "lock-up" if the Branch Count value is greater than the combined capacities of the Instruction Buffer and Fetch Unit Pipeline.

Lastly, the most restrictive model for Branches can be chosen where all taken Branch instructions are required to hold up in the Instruction Buffer until the last branch-dependent instruction has been fetched into the Instruction Buffer. These alternative models for Branch instruction implementations are provided to enable an assessment to be made of the benefits to be gained by using the most powerful model where there is minimal hold-up in dispatching instructions.

# 11.1.4 Functional Capability

As discussed in earlier sections, the Simulator has a number of "pipes" that are used as conduits to route instructions in parallel to the appropriate Functional Units. A user can set the number of pipes available to the machine, up to a maximum of 32. The common pool of Functional Units is then accessed by instructions from the pipes on a first-come first-served basis to ensure inorder dispatch of instructions. The number and type of Functional Units comprising the

common pool can be individually specified by the user via menu options, or a pre-defined set of parameters can be selected for a frequently used model. An ability to vary the mix of Functional Units, and to select pipelined or non-pipelined versions for most types of Functional Units, allows a number of interesting Simulator models to be tested and results compared for different runs of a particular program.

### 11.2 Tracing Facilities

The Simulator offers several methods for following the progress of a program as it is executed on the machine model. When the menu option to run a program is selected, a number of prompts are given to the user that will determine what information will be shown on the screen during the run. If the "trace" option is activated the user can specify the Instruction Cache address from which the trace is to start, or give the number of clock cycles that are to be executed before tracing begins.

Once the tracing commences the contents of the "pipes" are shown each cycle, along with the contents of the Instruction Buffer and the Fetch Unit. In addition, various procedures that are activated in the Simulator program will give the user information relating to the issuing of instructions, data dependency tests and results of the latest computations taking place in the Functional Units. A parameter can be set by the user that calls for a "full report" when in trace mode and this gives additional information for each machine cycle. In particular, the current state of all the Functional Units can be seen showing all instructions in their different pipeline stages together with the new result value and the final destination register or memory address. The full report facility was extremely useful in debugging the Simulator program itself and will be a valuable tool in tracing a scheduled program that is not performing as expected, possibly due to a scheduling error.

As well as explicitly requesting the trace mode, the user can ask the Simulator to stop after an error is encountered and then enter the trace mode for the remainder of the program run. This facility is useful when debugging code that runs successfully for a large number of cycles before an error occurs.

An option exists that will record the results of a trace in a specified file so that a hard-copy listing can be produced to help analyse the Simulator run. This recorded trace contains a cycle-by-cycle account of which instructions were successfully issued to Functional Units, together with a snapshot of the current contents of the Main Integer and Boolean Register files.

#### 11.3 Statistical Data

During a program run on the Simulator a large amount of statistical data is being recorded to give a profile of the program and the way in which the machine's resources have been utilised. The user can display or print out this information via the menu options. The analysis includes a breakdown of the instructions dynamically executed according to the instruction type. Branch instructions are categorised into conditional or unconditional branches, with figures showing the percentage of conditional branches that were actually taken.

The total number of machine cycles used is displayed as well as a count of the total number of instructions that completed execution. The number of instructions dispatched to Functional Units is recorded separately and may not tally with the total for those that complete execution. This discrepancy is due to instructions failing to meet the conditions required for execution whilst in a Functional Unit or being squashed because of WAW dependencies.

The abstract Instruction Cache used by the Simulator serves as a useful data structure for recording the dynamic execution of each of the instructions in the program by simply adding a counter field that is incremented by the Functional Units when they complete execution. The modified contents of the Instruction Cache can then be displayed or printed out to give a profile of the program's dynamic behaviour.

The usage of each pipe is shown as a percentage of all instructions executed so that the user can see the likely effect of increasing or decreasing the number of pipes in a subsequent program run. Similarly, figures are given for each of the Functional Units to show the percentage of instructions of the specified type that were executed in the individual units provided. In addition, various counters are used to record the number of times that instructions of different types were unable to be issued due to a resource being unavailable. These figures give an indication of the likely loss in performance due to an over-restrained machine model being specified.

Careful analysis of the statistical data can result in machine parameters being altered to obtain maximum utilisation from a minimal set of simulated hardware functions when running the benchmark programs, without undue loss in performance. It is hoped that this "fine-tuning" of the Simulator model will result in a machine model being developed that is far simpler than the maximum allowed for in the range of Simulator parameters. Such a Minimal Superscalar could then be studied in more detail with regard to circuit complexity and signal timing arising from actual hardware implementations [2].

The Simulator program makes use of the concept of object orientation by separating out some of the data structures into separate modules, along with all the procedures required to manipulate them. The main Simulator program has only an abstract view of structures such as the Instruction Buffer so that the actual implementation can be changed in the future, to take account